В состав ПИТ входят три шестнадцатиразрядных вычитающих счетчика с частотой счета до 2МГц. Каждый таймер может работать в одном из следующих шести программно-заданных режимов независимо от других как в двоичном коде, так и в двоично-десятичном:

- режим 0 – прерывание по окончанию счета;

- режим 1 – программируемый одновибратор;

- режим 2 – генератор частоты;

- режим 3 – генератор прямоугольных импульсов;

- режим 4 – программная задержка строба;

- режим 5 – аппаратная задержка строба.

В разрабатываемой МПС ПИТ необходим для формирования выходных воздействий (Y1, Y2, Y3 и Y5) и для синхронизации ПСА. Для формирования сигналов Y1 и Y5 используем канал 0, для формирования сигналов Y2 и Y3 – канал1, а для синхронизации ПСА – канал 2. При этом изначально каналы 0 и 1 программируются для работы в режиме 1, а канал 2 и канал 0 для формирования сигнала Y5 – в режим 3.

АЦП 1113ПВ1 – однокристальный функционально-законченный совместимый с микросхемами, работающими с ТТЛ уровнями АЦП последовательного приближения. Имеет внутренний источник опорного напряжения, генератор тактовых импульсов и компаратор напряжения. Для включения АЦП необходимы только источник питания и формирователь преобразования. Для получения цифрового представления аналогового сигнала через ППА подаем сигнал на вход CS АЦП. Об окончании преобразования АЦП сигнализирует установкой логической единицы на выходе RDY, который также подключен к МПС с помощью ПСА. Максимальное время преобразования – 30 мкс.

ЦАП К572ПА1 – однокристальный двенадцатиразрядный ЦАП с максимальным временем установки выходного тока – 3,5 мкс.

В качестве ГТ будем использовать однокристальный микроконтроллер КМ1816ВЕ51. В состав микроконтроллера входят следующие элементы:

1) процессор – однобайтное АЛУ и схемы аппаратной реализации команд умножения и деления;

2) стираемое ПЗУ программ – четыре килобайта;

3) ОЗУ данных – 128 байт;

4) два шестнадцатиразрядных таймера-счетчика

5) четыре программируемых порта

6) блок двухуровневых прерываний от пяти источников;

7) асинхронный канал дуплексного последовательного ввода-вывода информации со скоростью не менее 375 бит/с;

8) генератор тактовых импульсов;

9) схема синхронизации и управления.

Микроконтроллер взаимодействует с вычислительными каналами через свои порты и через линии запросов прерываний. Выполняя функции генератора тестов, микроконтроллер циклически отключает от ОУ МПС и производит тестирование обоих каналов, имитируя работу АЦП и регистра двоичных входных значений. Микроконтроллер в течение нескольких циклов тестирования производит эмуляцию поступления к МПС всего множества входных значений. Более подробно работа микроконтроллера КМ1816ВЕ51 в качестве генератора тестов будет рассмотрена ниже.

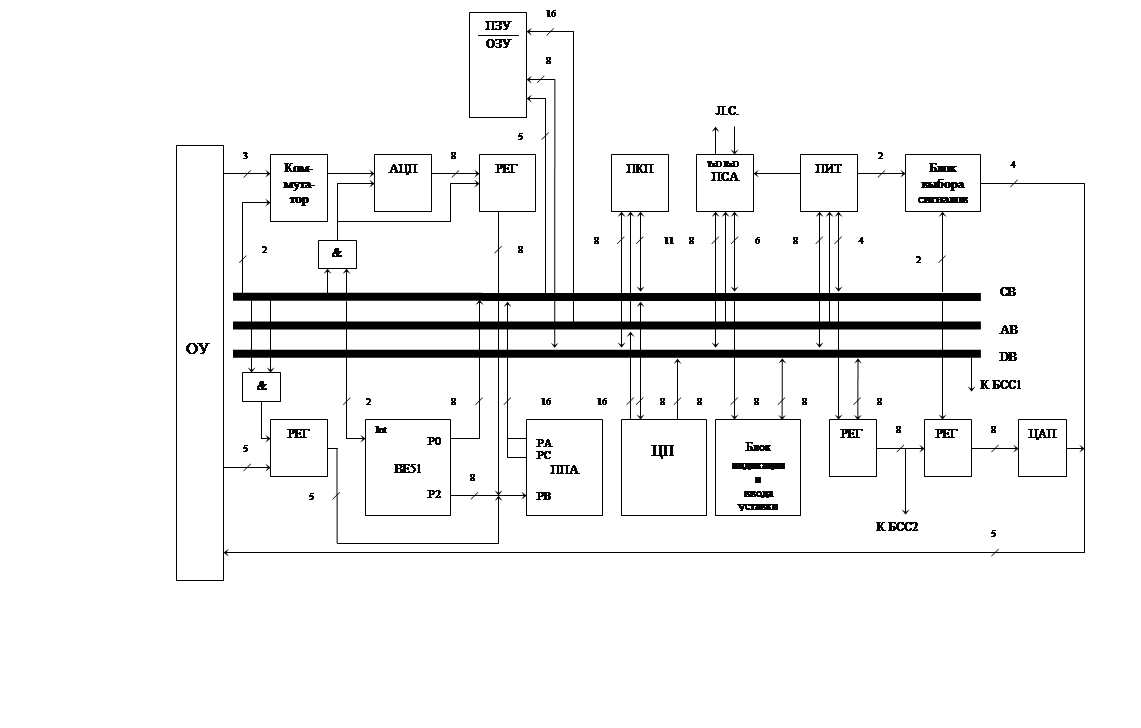

Так как мы имеем в проектируемой микропроцессорной системе два идентичных вычислительных канала ВК1 и ВК2, то достаточно привести одну функциональную схему. Функциональная схема вычислительного канала представлена на рисунке 2.

|

Обе безопасные схемы сравнения БСС1 и БСС2 также как и вычислительные каналы имеют одинаковую структуру, различие лишь в том, что БСС1 подключается к шинам данным ВК1 и ВК2, а БСС2 – к их выходным регистрам. Функциональная схема безопасной системы сравнения представлена на рисунке 3.

Основу безопасной системы сравнения составляют самопроверяемые тестеры (СПТ) 2/4. Эти элементы предназачены для проверки того, являются ли контролируемые коды равновесными. В случае удовлетворения этого условия на выходах СПТ присутствует парафазный сигнал. Если же код не равновесный или произошел отказ какого-либо элемента включенного в СПТ, то на выходах – непарафазный сигнал [2].

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.