Лабораторная работа №3

ПРОЕКТИРОВАНИЕ ПОДСИСТЕМЫ РЕАЛЬНОГО ВРЕМЕНИ

Цель работы. Получить практические навыки в проектировании подсистем реального времени и систем синхронизации устройств, реализуемых на базе ПЛИС.

Задание:

Декрементный 4 разрядный двоично-десятичный счетчик, предделитель входной частоты на 12

Текстовое описание передаточной функции:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity lab_3 is

Port ( X : in STD_LOGIC;

Y1 : out STD_LOGIC_VECTOR (3 downto 0);

Y2 : out STD_LOGIC_VECTOR (3 downto 0);

Y3 : out STD_LOGIC_VECTOR (3 downto 0);

Y4 : out STD_LOGIC_VECTOR (3 downto 0));

end lab_3;

architecture Behavioral of lab_3 is

signal count1 : std_logic_vector(3 downto 0) :="0001";

signal count2 : std_logic_vector(3 downto 0) :="0001";

signal count3 : std_logic_vector(3 downto 0) :="0001";

signal count4 : std_logic_vector(3 downto 0) :="0000";

signal clk : std_logic_vector(3 downto 0):="0000";

begin

process (X)

begin

if X='1' and X'event then

clk<=clk + 1;

if clk="1100" then

clk<="0000";

count1<=count1 - 1;

if count1="0000" then

count1<="1001";

count2<=count2 - 1;

if count2="0000" then

count2<="1001";

count3<=count3 - 1;

if count3="0000" then

count3<="1001";

count4<=count4 - 1;

if count4="0000" then

count4<="1001";

end if;

end if;

end if;

end if;

end if;

end if;

end process;

Y1<=count1;

Y2<=count2;

Y3<=count3;

Y4<=count4;

end Behavioral;

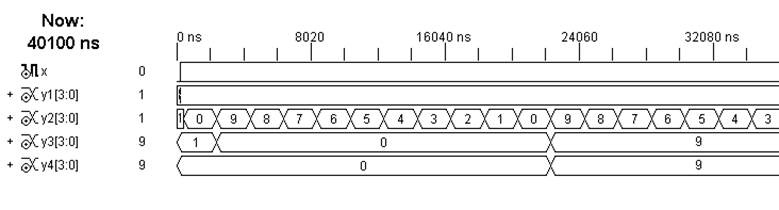

Рисунок 1 – Работа двоично-десятичного счетчика без предделителя

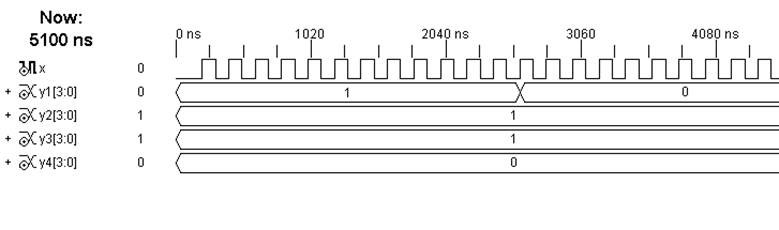

Рисунок 2 – Работа двоично-десятичного счетчика с предделителем

Вывод: Получил практические навыки в проектировании подсистем реального времени и систем синхронизации устройств, реализуемых на базе ПЛИС. Реализовал декрементный четырехразрядный двоично-десятичный счетчик, а также предделитель тактовой частоты на 12.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

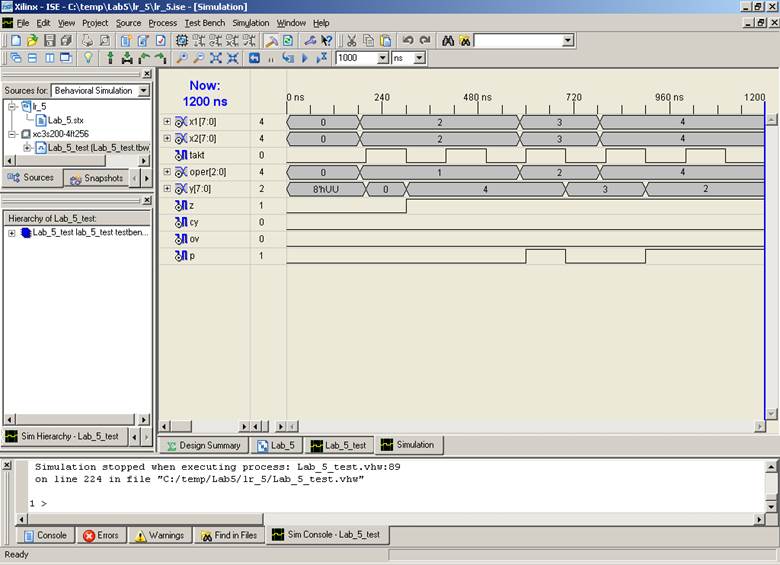

entity Lab_5 is

Port ( X1 : in STD_LOGIC_VECTOR (7 downto 0);

X2 : in STD_LOGIC_VECTOR (7 downto 0);

takt : in STD_LOGIC;

Oper : in STD_LOGIC_VECTOR (2 downto 0);

Y : out STD_LOGIC_VECTOR (7 downto 0);

Z : out STD_LOGIC :='0';

CY : out STD_LOGIC :='0';

OV : out STD_LOGIC :='0';

P : out STD_LOGIC :='0');

end Lab_5;

architecture Behavioral of Lab_5 is

signal temp: std_logic_vector(7 downto 0):="00000000";

signal overflow: std_logic_vector(15 downto 0):="0000000000000000";

signal last: std_logic:='0';

begin

process(takt)

variable k: integer;

variable t: integer;

variable res: integer;

begin

t:=conv_integer(unsigned(X1));

k:=conv_integer(unsigned(X2));

if Oper="001" then

res:=k*t;

temp <= std_logic_vector( conv_unsigned ( res, 8 ) );

Y <= temp;

P <= temp(0);

overflow <= std_logic_vector(conv_unsigned (res,16));

if temp(7 downto 0)="00000000" then

Z <= '0';

else

Z <= '1';

end if;

if overflow(15 downto 8)="00000000" then

OV <= '0';

else

OV <='1';

end if;

end if;

if Oper="010" then

temp<=X1 and X2;

Y<=temp;

P<= temp(0)xor temp(1)xor temp(2)xor temp(3)xor temp(4)xor temp(5)xor temp(6)xor temp(7);

if temp(7 downto 0)="00000000" then

Z <= '0';

else

Z <='1';

end if;

end if;

if Oper="100" then

last<=X1(0);

temp(6 downto 0)<=X1(7 downto 1);

temp(7)<=last;

Y<=temp;

CY<=last;

P<= temp(0)xor temp(1)xor temp(2)xor temp(3)xor temp(4)xor temp(5)xor temp(6)xor temp(7);

end if;

end process;

end Behavioral;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.