Лабораторная работа №9

(4 Часа)

Проектирование и моделирование релейных и иерархических схем в САПР OrCAD

Цель работы: Изучить методы и приёмы проектирования и динамического моделирования в САПР релейных и иерархических схем

Перед выполнением задания необходимо тщательно разобрать и понять работу проектируемых и моделируемых схем!

При необходимости обратиться к литературе и справочникам по схемотехнике.

Для Заданий 1 и 2 один вариант для всех студентов.

ЗАДАНИЕ 1. Подготовка исходной схемы

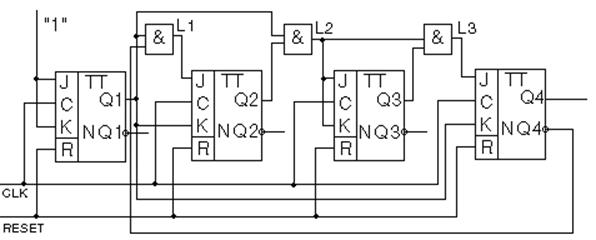

1.1 Запустите графический редактор и нарисуйте в нём цифровую схему счётчика согласно рис.1.

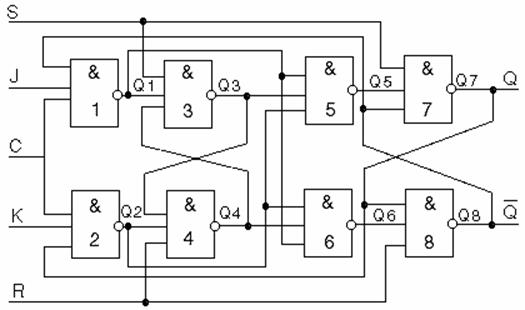

Рисунок 1. Счетчик по модулю 10, построенный на JK-триггерах с запрещающими

связями

1.2. Для подготовки схемы найдите соответствующие зарубежные аналоги компонентов, отыщите их в библиотеках пакета и разместите их в рабочем окне редактора. В качестве JK-триггеров, например, можно использовать элементы 7473 или 7476.

1.3 Выполните все необходимые соединения.

1.4 Пронумеруйте (сделайте необходимую маркировку) цепи для всех генераторов внешних воздействий.

ЗАДАНИЕ 2. Задайте внешние воздействия для моделирования

2.1 Подключите маркёры к цепям, которые вы собираетесь контролировать.

2.2 На генераторах внешних воздействий задайте для каждого входного сигнала его временную диаграмму.

2.3 Задайте вид анализа Transient и время моделирования.

2.4 Запустите схему на моделирование.

2.5 Сохраните результаты моделирования для подготовки отчёта.

ЗАДАНИЕ 3. Моделирование работы активных фильтров

3.1 Подготовить чертёж активного фильтра в соответствии с вариантом задания. Номиналы элементов схемы округлять до целых.

Операционные усилители выбрать самостоятельно из библиотек OPAMP, Tex-Instr, Maxim, Apex или Anlg_dev. Например, из библиотеки OPAMP можно воспользоваться одним из следующих ОУ: AD648B, LF412, TL082 или UA772.

ВНИМАНИЕ! Внимательно следите за правильностью подключения операционных усилителей. Не перепутайте полярность (+ и – источников питания) при подключении в схеме.

Примерный вид чертежа приведён на рис.2.

Рисунок 2. Один из вариантов схемы задания 3.

3.2 Подать на вход схемы сигнал от источника импульсного напряжения по форме близкий к прямоугольному и получить переходные характеристики, а также спектральные характеристики входного и выходного импульсов. Ожидаемый вид переходной функции для активного фильтра низких частот представлен на рис.3.

Рисунок 3. Переходная функция для активного фильтра, приведённого на рис.2.

3.3 Подать на вход схемы сигнал от источника гармонических сигналов VAC и получить частотные характеристики схемы. Ожидаемый вид частотных характеристик для активного фильтра низких частот представлен на рис.4 и рис.5.

Рисунок 4. График АЧХ фильтра, приведённого на рис.2.

Рисунок 5. График ФЧХ фильтра, приведённого на рис.2

3.4 По итогам моделирования сделать вывод о типе моделируемого фильтра и его характеристиках.

ЗАДАНИЕ 4. Проектирование дешифраторов

4.1 Самостоятельно спроектировать дешифратор с двумя выходами согласно варианта задания, подключаемый к схеме счётчика, спроектированного в задании 1 настоящей лабораторной работы.

Дешифратор должен фиксировать установку счётчика в одно из указанных состояний согласно задания.

Например (вариант №2), Выход1 дешифратора должен устанавливаться в состояние логической «1» при установке счётчика в состояние 2; в остальных случаях на выходе должно быть состояние логического «0». На Выходе2 дешифратора должно появляться состояние логической «1» при установке счётчика в состояние 8; в остальных случаях на этом выходе – логический «0».

Пример схемы со счётчиком (схема 74393) и дешифратором (схема 74154) приведён ниже на рисунке.

Рисунок 6. Схема двоичного счётчика с дешифратором

Моделирование показывает, что один из выходов дешифратора устанавливается в состояние логического «0» в зависимости от состояния счётчика U2A. Соответствующие выходы дешифратора могут управлять, например, RS-триггером, который в свою очередь может управлять релейным элементом. Диаграмма работы схемы приведена на рисунке ниже:

Рисунок 7. Диаграмма работы схемы, приведённой на рисунке 6

ЗАДАНИЕ 5. Проектирование релейных схем

5.1 Спроектировать релейную схему, которая:

- а) в исходном (начальном) состоянии подключает вход активного фильтра, спроектированного в задании 3, на «Землю»;

- б) при срабатывании Выхода1 дешифратора из задания 4 подключает на вход схемы фильтра источник синусоидального напряжения с частотой F1;

- в) при срабатывании Выхода2 дешифратора из задания 4 переключает на вход схемы фильтра источник синусоидального напряжения с частотой F2;

5.2 Выполнить моделирование схемы, убедиться в её работе согласно задания.

В качестве релейного элемента использовать ключ S, управляемый напряжением из библиотеки ANALOG. Управлять ключом можно через TTL-схему с открытым коллектором, например, инвертором 7405. Пример подобного включения показан на рисунке 8. На рисунке 9 приведены графики напряжений, которые иллюстрируют работу схемы.

Рисунок 8. Пример включения ключа, управляемого напряжением

Рисунок 9. Эпюры изменения напряжений схемы, приведённой на рисунке 8

ЗАДАНИЕ 6. Построение иерархических схем

6.1 Подготовить схему JK-триггера согласно его логической схеме, приведённой на рисунке 10.

Рисунок 10. Логическая схема JK-триггера

6.2 Оформить схему в виде иерархического блока.

6.3 Нарисовать схему счётчика из собственных иерархических блоков.

6.4 Выполнить моделирование схемы, результаты сравнить с результатами моделирования Задания 1.

6.5 Оформить схемы фильтра, дешифратора и релейной схемы в отдельные иерархические блоки. Подготовить схему согласно Задания 5 из разработанных в настоящем Задании иерархических блоков и выполнить моделирование её работы. Сравнить с результатами, полученными в Задании 5.

7 Подготовить отчёт по работе. В отчёте привести спроектированные схемы и результаты их моделирования, объясните полученные результаты, сделать доказательные выводы по работе.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.