функциональной схеме микросхемы обозначается выполняемая функция. Внизу пишется емкость в битах, иногда добавляется размер слова.

В правом верхнем углу указывается состояние выходных шин, например:

![]() - выход

имеет три состояния: 0, 1, ∞.

- выход

имеет три состояния: 0, 1, ∞.

1 Способы организации элементов памяти

В зависимости от способа организации элементов памяти, различают следующие технические решения: поразрядная и пословная выборка информации.

Если каждый элемент памяти содержит только одну ячейку памяти, которая адресуется индивидуально, в нее отдельно может быть записана и из нее может быть считана информация (поразрядная выборка).

Пример обозначения информационной емкости: объемом памяти 1024 ·1 или 1 K (1024 элементов памяти, содержащих по 1 ячейке).

В случае, когда элемент памяти содержит несколько ячеек, то при обращении к нему может одновременно записываться или считываться определенный объем информации (пословная выборка).

Пример обозначения информационной емкости: объемом памяти 1024 ·8 или 8 K (1024 элементов памяти, содержащих по 8 ячеек).

В зависимости от способа поиска информации, различают память с одномерной (2D) и двухмерной (3D) адресацией.

1.1 Память 2D

Память по типу организации 2D включает в себя:

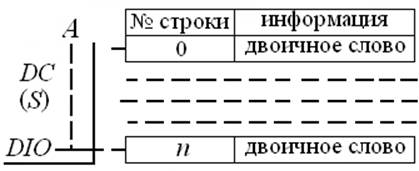

- матрицу элементов памяти (ЭП), которая представляет собой последовательность строк, имеющих свой индивидуальный адрес. В каждой строке может записываться двоичное число из n бит;

- дешифратор адреса, преобразующий двоичный код адреса строки A в сигнал управления для обеспечения доступа к ней (рис. 1);

- параллельные регистры для временного хранения входных и выходных данных.

Сигналы с адресной шины в параллельном коде поступают на регистр, что обеспечивает работу памяти в случае смены информации на шине.

Адрес строки (A), в которую надо записать или из которой требуется считать информацию, из регистра передается в дешифратор адреса. Он, в свою очередь, выбирает в матрице требуемые элементы памяти строки в соответствие с сигналом Ai. Дешифратор, в данном случае, позволяет сократить количество выводов микросхемы (рис. 2).

Например, 10-канальный двоичный адресный вход в микросхему памяти позволяет определить 1024 различных адресов в ней.

Рис. 1 Функциональная схема выбора строки

Дешифратор DC, на рисунке изображенный в виде переключателя S, соединяетсовмещенные вход-выход DI0 согласно коду адреса A с выбранной строкой.

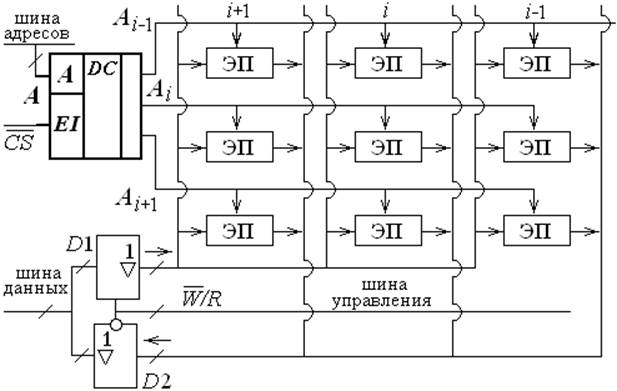

На рис. 2 представлена функциональная схема памяти 2D.

Рис. 2 Функциональная схема памяти 2D

При записи, информационный сигнал с шины данных параллельным кодом передается через буферы D1 в элементы памяти. Буферы D2 отключены управляющим сигналом.

В случае считывания, информационный сигнал из элементов памяти параллельным кодом, через буферы D2 поступает на шину данных. Буферы D1 отключены.

Микросхема работает при поступлении по шине управления на вход CS сигнала логического нуля.

Тип операции (запись, чтение) определяется сигналом шины управления W/R.

Память обладает небольшой информационной емкостью вследствие сложности дешифратора.

1.2 Память 3D

Память по типу организации 3D включает в себя:

- матрицу элементов памяти, содержащей n квадратных подматриц, где n – ширина выборки;

- подматрицы (рис. 3), в которые записывается или из которых считывается значение одного из разрядов всех двоичных слов, находящихся в памяти;

- дешифратор адреса X, преобразующий первую половину двоичного кода

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.