этот сигнал должен передаваться при достижении состояния 1001.

![]() .

.

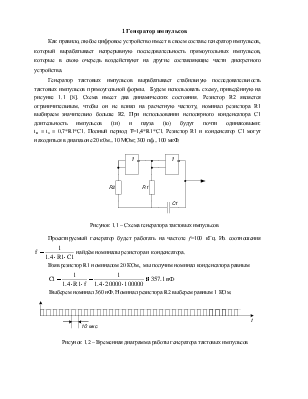

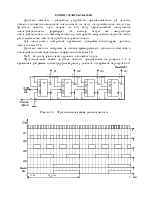

Временная диаграмма работы счетчика за один цикл приведена на рисунке 2.2.

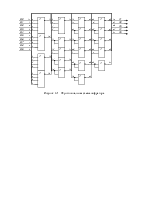

Рисунок 2.1 – Схема параллельно-последовательного суммирующего счетчика

Рисунок 2.2 – Временная диаграмма работы счетчика

3 Синтез шифратора

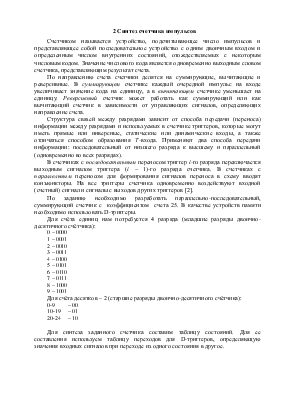

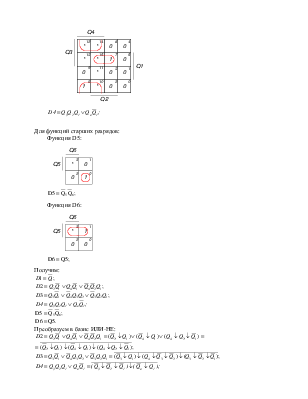

Шифратор служит для преобразования цифр, задаваемых сигналом “1” на индивидуальных шинах, в параллельный код. Синтез подобных устройств фактически сводится к представлению цифр в виде суммы чисел, каждое из которых равно 2k , где k=0, 1, 2,…[2].

Согласно заданию на выходе шифратора необходимо получить кодовые комбинации кода “3а+2”. Входом ДУ является вход шифратора. Для синтеза шифратора составим таблицу 3.1, в которую занесем цифры от 0 до 9 и соответствующие им кодовые комбинации кода “3а+2”, а затем полученные формулы переведем в базис ИЛИ-НЕ.

Таблица 3.1 - Таблица истинности шифратора

|

Кодовые комбинации (“3а+2”) |

Десятичный эквивалент |

||||

|

Y5 |

Y4 |

Y3 |

Y2 |

Y1 |

Xi |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

2 |

|

0 |

1 |

0 |

1 |

1 |

3 |

|

0 |

1 |

1 |

1 |

0 |

4 |

|

1 |

0 |

0 |

0 |

1 |

5 |

|

1 |

0 |

1 |

0 |

0 |

6 |

|

1 |

0 |

1 |

1 |

1 |

7 |

|

1 |

1 |

0 |

1 |

0 |

8 |

|

1 |

1 |

1 |

0 |

1 |

9 |

По данной таблице истинности запишем СКНФ и переведем в базис ИЛИ-НЕ с учетом наличия двух-, трех- и четырехвходовых элементов в используемой серии микросхем:

![]() ;

;

![]()

![]()

![]()

![]()

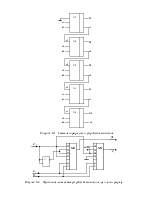

По полученным функциям строим шифратор (рисунок 3.1). На рисунке 3.2 представлена временная диаграмма работы шифратора.

Рисунок 3.1 – Функциональная схема шифратора

Рисунок 3.2 – Временная диаграмма работы шифратора

4 Синтез делителя частоты

Делитель частоты - дискретное устройство, предназначенное для деления общего количества импульсов поступивших на вход, на произвольное число кдел. Делитель частоты, при подаче на его вход периодической импульсной последовательности, формирует на выходе такую же импульсную последовательность, но имеющую частоту повторений импульсов в заданное число раз (кдел) меньше, чем по входной последовательности.

Для наглядности построения временных диаграмм синтезируем делитель частоты с кдел = 16.

Делитель частоты построим на основе суммирующего двоичного счетчика с последовательным переносом и коэффициентом счёта 16.

На S – входы будем подавать уровень логического нуля.

Функциональная схема делителя частоты представлена на рисунке 4.1, а временная диаграмма, иллюстрирующая работу делителя, изображена на рисунке 4.2

Рисунок 4.1 – Функциональная схема делителя частоты

Рисунок 4.2 – Временная диаграмма работы делителя частоты

5 Синтез регистра

Регистрами называются устройства, выполняющие функции приема, хранения, логической обработки и передачи информации. Информация в регистре хранится в виде числа (слова), представленного комбинацией сигналов "0" и "1". Каждому разряду числа, записываемому в регистр, соответствует свой разряд регистра. Обычно регистры выполняются на триггерах. Триггер с номером i является i-м разрядом регистра и представляет i-й разряд двоичного слова х1, х2, х3, ..., хn, где хi (i = 1, 2, 3,..., n) – двоичное значение переменной данного разряда, равное 0 или 1. Число возможных состояний n-разрядного регистра равно 2n. Для сокращения записи двоичного числа, отображающего состояние регистра, иногда используется восьмеричное и шестнадцатеричное представление двоичных чисел [2].

По заданию необходимо спроектировать параллельный регистр сдвига, на который будут поступать кодовые комбинации с выходов шифратора CD, тактируемый импульсами ГИ. Так как выход шифратора пятиразрядный, то регистр будет содержать пять D-триггеров.

Рисунок 5.1 – Функциональная схема регистра

Рисунок 5.2 – Временная диаграмма работы регистра

6 Синтез устройства вычитания

Двоичные вычитатели выполняют арифметическую операцию вычитания двоичных чисел и используются преимущественно в арифметико-логических

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.