32. Построить ФАЛ ![]() на базе синхронных мультиплексоров с двумя

адресными входами.

на базе синхронных мультиплексоров с двумя

адресными входами.

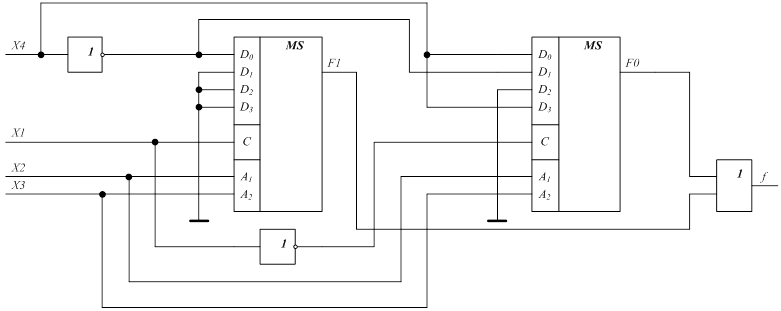

Использование синхронизирующего входа мультиплексора. Наличие синхронизирующего входа позволяет расширить возможности реализации ФАЛ на мультиплексорах.

Приведем алгоритм реализации ФАЛ k переменных с использованием двух мультиплексоровс синхронизирующими входами:

1) написание заданной ФАЛ в ДНФ;

2) разложение заданной ФАЛ по переменной с индексом i;

3) нахождение выражения функций F0 и F1 переменных (k – 1);

4) реализация ФАЛ F0 и F1 на мультиплексорах с (k – 2) управляющими входами. Сигналы, соответствующие (k – 2) переменным, подать параллельно на управляющие входы обоих мультиплексоров;

5) подача сигнала, соответствующего переменной с индексом i на стробирующий вход первого мультиплексора, реализующего ФАЛ F1, и через инвертор – на стробирующий вход второго мультиплексора, реализующего ФАЛ F0;

6) объединение прямых выходов мультиплексоров, используя элемент ИЛИ.

Построить схему на мультиплексорах с двумя

управляющими и стробирующими входами для ФАЛ четырех переменных ![]()

Разложим ФАЛ по переменной ![]() :

:![]() , где

, где

![]()

![]() .

.

Величины F0 и F1 являются функциями трех переменных, и могут быть реализованы на мультиплексорах с двумя управляющими входами на основании вышеприведенного алгоритма. Разложим функции F0 и F1 по Х2 и Х3:

![]()

![]()

Если на синхронизирующие входы мультиплексоров, реализующих F0 и F1, подать сигналы, соответствующие переменной, дизъюнкция выходных функций на прямых выходах обоих мультиплексоров реализует заданную ФАЛ.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.