5.Выбор элементной базы и описание микросхем

Для построения принципиальных схем ПУ и КП будем использовать в основном микросхемы ТТЛШ (микросхемы транзисторно - транзисторной логики со структурой Шотки), т.к. их отличает следующее:

Ø высокая надёжность;

Ø высокое быстродействие;

Ø малые габариты;

Ø независимость работы от положения микросхемы в пространстве.

При построении принципиальной схемы были использованы описанные ниже микросхемы.

Восьмиразрядный шифратор приоритетов – 133ИВ1

( 8-общий, 16 - +5В )

Таблица истинности.

|

Е |

I7 |

I6 |

I5 |

I4 |

I3 |

I2 |

I1 |

I0 |

А2 |

А1 |

А0 |

G |

ED |

|

1 |

X |

1 |

1 |

1 |

1 |

1 |

1 |

X |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

X |

X |

X |

X |

X |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

1 |

Выходной сигнал шифратора G является сигналом наличия возбуждённых информационных разрядов. Так как активным уровнем в ИС является низкий, то G следует понимать, как сигнал присутствия на входе, хотя бы одного нуля. У казанный сигнал может быть использован для разрешения работы следующих узлов, выходной код шифратора является входным. Сигнал ЕО напротив является сигналом отсутствия возбужденных разрядов и при каскадировании играет роль разрешающего для смежных каскадов.

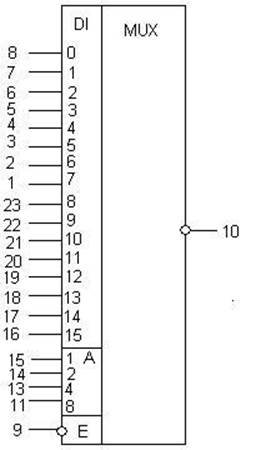

16-разрядный инвертирующий стробирующий мультиплексор с адресным селектором – 133КП1.

( 12-общий, 24 - +5В )

Таблица истинности.

|

А8 |

А4 |

А2 |

А1 |

Е |

Выход |

|

X |

X |

X |

X |

X |

1 |

|

0 |

0 |

0 |

0 |

1 |

DI0 |

|

0 |

0 |

0 |

1 |

0 |

DI1 |

|

0 |

0 |

1 |

0 |

0 |

DI2 |

|

0 |

0 |

1 |

1 |

0 |

DI3 |

|

0 |

1 |

0 |

0 |

0 |

DI4 |

|

0 |

1 |

0 |

1 |

0 |

DI5 |

|

0 |

1 |

1 |

0 |

0 |

DI6 |

|

0 |

1 |

1 |

1 |

0 |

DI7 |

|

1 |

0 |

0 |

0 |

0 |

DI8 |

|

1 |

0 |

0 |

1 |

0 |

DI9 |

|

1 |

0 |

1 |

0 |

0 |

DI10 |

|

1 |

0 |

1 |

1 |

0 |

DI11 |

|

1 |

1 |

0 |

0 |

0 |

DI12 |

|

1 |

1 |

0 |

1 |

0 |

DI13 |

|

1 |

1 |

1 |

0 |

0 |

DI14 |

|

1 |

1 |

1 |

1 |

0 |

DI15 |

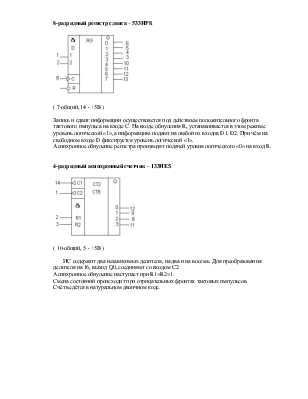

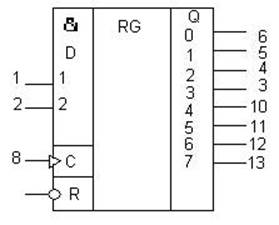

8-разрядный регистр сдвига – 533ИР8.

( 7-общий, 14 - +5В )

Запись и сдвиг информации осуществляется под действием положительного фронта тактового импульса на входе С. На входе обнуления R, устанавливается в этом режиме уровень логической «1», а информацию подают на любой из входов D1, D2. При чём на свободном входе D фиксируется уровень логической «1».

Асинхронное обнуление регистра производят подачей уровня логического «0» на вход R.

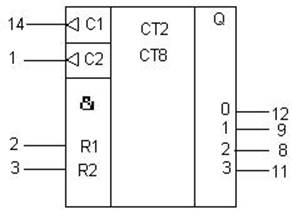

4-разрядный асинхронный счетчик – 133ИЕ5.

( 10-общий, 5 - +5В )

ИС содержит два независимых делителя, на два и на восемь. Для преобразования делителя на 16, выход Q0, соединяют со входом С2.

Асинхронное обнуление наступает при R1=R2=1.

Смена состояний происходит при отрицательных фронтах тактовых импульсов.

Счёт ведётся в натуральном двоичном коде.

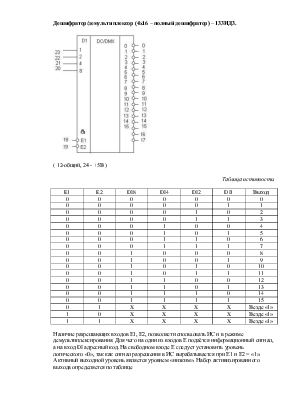

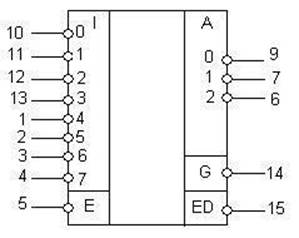

Дешифратор/демультиплексор (4x16 – полный дешифратор) – 133ИД3.

( 12-общий, 24 - +5В )

Таблица истинности.

|

E1 |

E2 |

DI8 |

DI4 |

DI2 |

DI1 |

Выход |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

2 |

|

0 |

0 |

0 |

0 |

1 |

1 |

3 |

|

0 |

0 |

0 |

1 |

0 |

0 |

4 |

|

0 |

0 |

0 |

1 |

0 |

1 |

5 |

|

0 |

0 |

0 |

1 |

1 |

0 |

6 |

|

0 |

0 |

0 |

1 |

1 |

1 |

7 |

|

0 |

0 |

1 |

0 |

0 |

0 |

8 |

|

0 |

0 |

1 |

0 |

0 |

1 |

9 |

|

0 |

0 |

1 |

0 |

1 |

0 |

10 |

|

0 |

0 |

1 |

0 |

1 |

1 |

11 |

|

0 |

0 |

1 |

1 |

0 |

0 |

12 |

|

0 |

0 |

1 |

1 |

0 |

1 |

13 |

|

0 |

0 |

1 |

1 |

1 |

0 |

14 |

|

0 |

0 |

1 |

1 |

1 |

1 |

15 |

|

0 |

1 |

X |

X |

X |

X |

Везде «1» |

|

1 |

0 |

X |

X |

X |

X |

Везде «1» |

|

1 |

1 |

X |

X |

X |

X |

Везде «1» |

Наличие разрешающих входов Е1, Е2, позволяет использовать ИС и в режиме демультиплексирования. Для чего на один из входов Е подаётся информационный сигнал, а на вход DI адресный код. На свободном входе Е следует установить уровень логического «0», так как сигнал разрешения в ИС вырабатывается при Е1 и Е2 = «1».

Активный выходной уровень является уровнем «низким». Набор активизированного выхода определяется по таблице

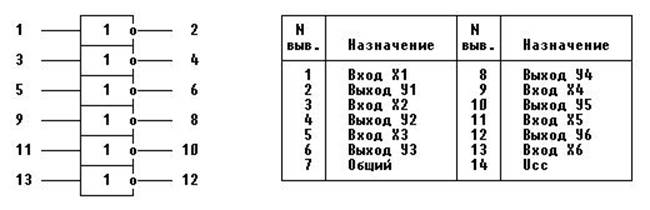

Логический элемент “НЕ” – КР1554ЛН1

Асинхронный R-S

триггер – К564ТР2

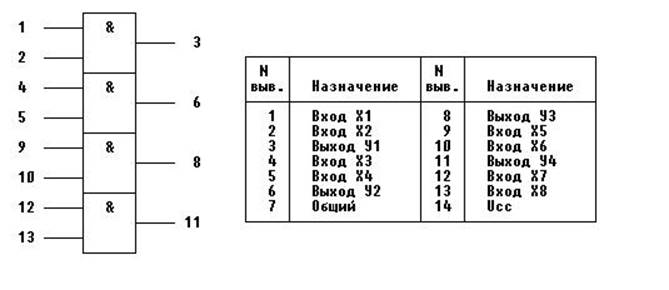

Четыре элемента И. КР1554ЛИ1

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.