Государственное образовательное учреждение высшего профессионального образования

«ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ» МИНИСТЕРСТВА ПУТЕЙ СООБЩЕИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Ройтман С.Я.

Золотов М.В.

Методические указания

к выполнению лабораторной работы №8

2004

Цель работы – изучение действия нескольких типов интегральных триггеров: RS-триггера на логических элементах ИЛИ-НЕ и И-НЕ; тактируемого RS-триггера (RST-триггера); D-триггеров. Лабораторная работа выполняется при помощи пакета программ Workbench EDA 5.0

Триггеры представляют собой устройство, обладающее несколькими устойчивыми состояниями. В схемах, работающих с двоичными числами, применяются триггеры с двумя устойчивыми состояниями, одно из которых соответствует логическому нулю, другое – логической единице. Записанная в триггере информация сохраняется до тех пор, пока триггер не изменит своего входного состояния.

Управление триггером может быть асинхронным или тактируемым (синхронным). При асинхронным управлении триггер переключается сразу при поступлении сигналов управления. В тактируемых триггерах схема управления имеет дополнительные вход С (clock – синхронизация) для подачи тактовых импульсов через определенные интервалы времени. Тактовые импульсы разрешают схеме управления передать информацию к собственно триггеру и произвести переключение.

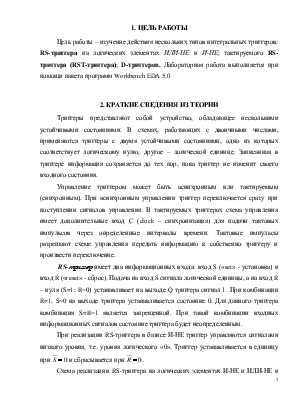

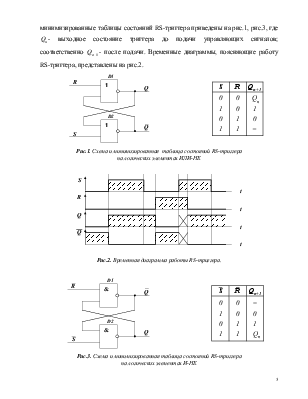

RS-триггер имеет два информационных входа: вход S («set» - установка) и вход R («reset» - сброс). Подача на вход S сигнала логической единицы, а на вход R – нуля (S=1; R=0) устанавливает на выходе Q триггера сигнал 1. При комбинации R=1, S=0 на выходе триггера устанавливается состояние 0. Для данного триггера комбинация S=R=1 является запрещенной. При такой комбинации входных информационных сигналов состояние триггера будет неопределенным.

При реализации RS-триггера в базисе И-НЕ

триггер управляются сигналами низкого уровня, т.е. уровня логического «0».

Триггер устанавливается в единицу при ![]() и

сбрасывается при

и

сбрасывается при ![]() .

.

Схема реализации RS-триггера на логических

элементах И-НЕ и ИЛИ-НЕ и минимизированные таблицы состояний RS-триггера

приведены на рис.1, рис.3, где ![]() - выходное состояние

триггера до подачи управляющих сигналов; соответственно

- выходное состояние

триггера до подачи управляющих сигналов; соответственно ![]() -

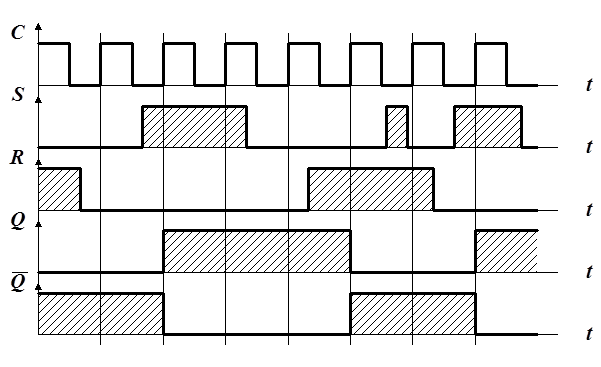

после подачи. Временные диаграммы, поясняющие работу RS-триггера,

представлены на рис.2.

-

после подачи. Временные диаграммы, поясняющие работу RS-триггера,

представлены на рис.2.

|

|

|

Рис.1. Схема и минимизированная таблица состояний RS-триггера на логических элементах ИЛИ-НЕ

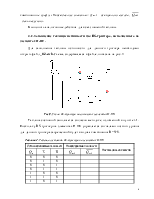

Рис.2. Временная диаграмма работы RS-триггера.

|

|

|

Рис.3. Схема и минимизированная таблица состояний RS-триггера на логических элементах И-НЕ

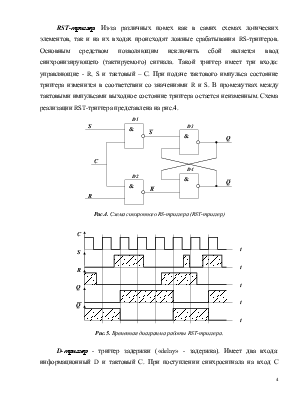

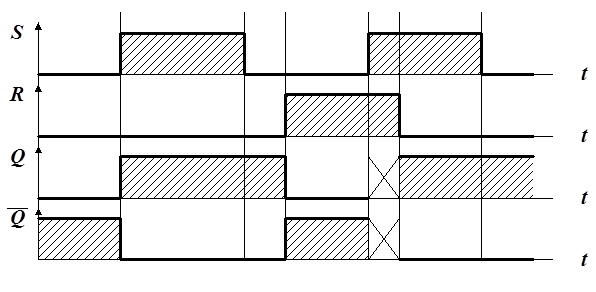

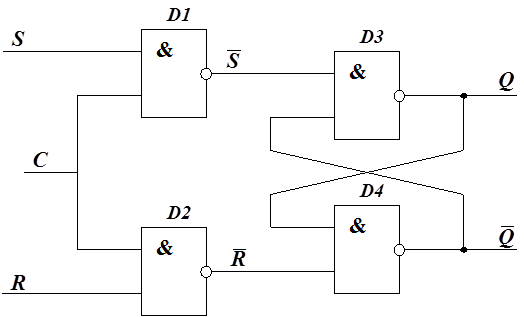

RST-триггер. Из-за различных помех как в самих схемах логических элементов, так и на их входах происходят ложные срабатывания RS-триггеров. Основным средством позволяющим исключить сбой является ввод синхронизирующего (тактируемого) сигнала. Такой триггер имеет три входа: управляющие - R, S и тактовый – С. При подаче тактового импульса состояние триггера изменится в соответствии со значениями R и S. В промежутках между тактовыми импульсами выходное состояние триггера остается неизменным. Схема реализации RST-триггера представлена на рис.4.

Рис.4. Схема синхронного RS-триггера (RST-триггер)

Рис.5. Временная диаграмма работы RSТ-триггера.

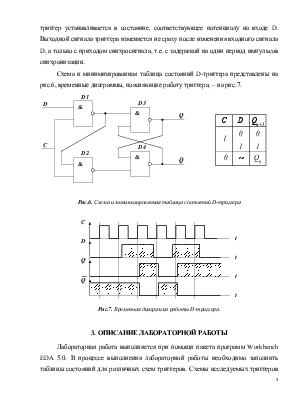

D-триггер - триггер задержки («delay» - задержка). Имеет два входа: информационный D и тактовый С. При поступлении синхросигнала на вход С триггер устанавливается в состояние, соответствующее потенциалу на входе D. Выходной сигнала триггера изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т.е. с задержкой на одни период импульсов синхронизации.

Схема и минимизированная таблица состояний D-триггера представлены на рис.6, временные диаграммы, поясняющие работу триггера, – на рис.7.

|

|

|

Рис.6. Схема и минимизированная таблица состояний D-триггера

Рис.7. Временная диаграмма работы D-триггера.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.