Министерство образования и науки Российской федерации

государственное образовательное учреждение высшего профессионального образования «Санкт-Петербургский государственный университет аэрокосмического приборостроения»

ОТЧЕТ

ЗАЩИЩЕН С ОЦЕНКОЙ

ПРЕПОДАВАТЕЛЬ

|

Бакшеева Ю.В. |

||||

|

должность, уч. степень, звание |

подпись, дата |

инициалы, фамилия |

|

ОТЧЕТ О ЛАБОРАТОРНОЙ РАБОТЕ №1 |

|

Элементарные логические функции |

по курсу: Цифровые устройства и микропроцессоры |

РАБОТУ ВЫПОЛНИЛ

|

СТУДЕНТ ГР. |

2946 |

Левин В.Ю. |

|||

|

подпись, дата |

инициалы, фамилия |

Санкт-Петербург 2011

1. Описание лабораторной установки

В данной лабораторной работе используются следующие элементы и инструменты из программы Electronic Workbench:

- панель источников питания (Sources):

”Ground” (земля)

“+Vcc Voltage Source” (источник напряжения)

“Clock” (генератор тактовых сигналов)

- панель пассивных элементов (Basic):

“Resistor” (проволочное сопротивление)

“Switch” (переключатель)

- панель логических элементов (Logic Gates)

- панель индикаторов (Indicators):

“Red Probe” (пробник логического уровня)

- панель инструментов (Instruments):

“Functional Generator” (генератор)

“Oscilloscope” (осциллограф)

1.1 Описание осциллографа

Программа Electronics Workbench имитирует аналог двухлучевого запоминающего осциллографа.

Для работы с осциллографом следует открыть панель инструментов (Instruments). Нажать левой кнопкой мыши и поместить прибор в рабочее поле. На рабочем поле появится уменьшенное изображение осциллографа. На этом изображении имеется четыре входных зажима:

- верхний правый зажим ¾ общий;

- нижний правый зажим ¾ вход синхронизации;

- левый и правый нижние зажимы представляют собой соответственно вход канала А (Channel A) и вход канала В (Channel В).

Двойным щелчком мыши по уменьшенному изображению открывается изображение передней панели осциллографа.

Для проведения измерений осциллограф нужно настроить:

- задать вид отображения сигналов. Нажать кнопку Y/T: по вертикальной оси откладывается напряжение, по горизонтальной оси ¾ время.

- установить нужный масштаб развёртки по времени (горизонтальная развертка) - на панели управления горизонтальной разверткой (масштабом времени) (Time base);

- установить нужный масштаб оси отображаемого напряжения. На поле А (Channel A) задать 5В/дел (V/div), на поле В (Channel В) задать 2В/дел (V/div);

- установить режим работы по входу для каждого канала. Кнопка АС - режим работы осциллографа с закрытым входом, кнопка DC - осциллограф переходит в режим с открытым входом.

- установить режим синхронизации: на панели Trigger нажать кнопку автоматический режим (Auto) - запуск осциллограммы производится автоматически при подключении осциллографа к схеме или при её включении.

2. Выполнение работы

2.1. Элементарные логические функции и логические элементы. Таблица истинности.

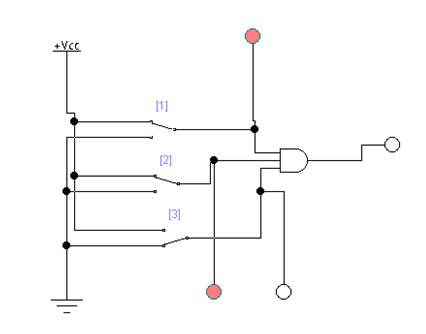

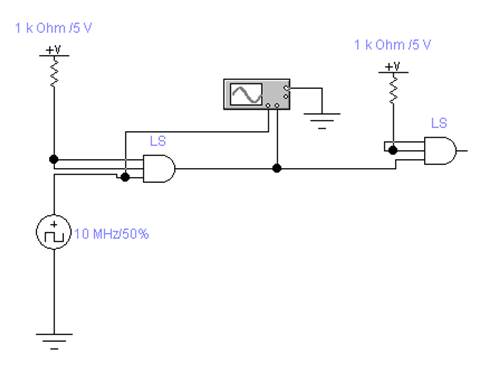

Для получения таблицы истинности собираем схему исследования логического элемента «3И», представленная на рисунке 1.

Рисунок 1 – Схема исследования логического элемента «3И».

Таблица истинности представлена в таблице 1.

Таблица 1.

|

X1 |

X2 |

X3 |

Y |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

2.2 Измерение времени задержки. Влияние нагрузки на быстродействие элементов ТТЛ и КМОП.

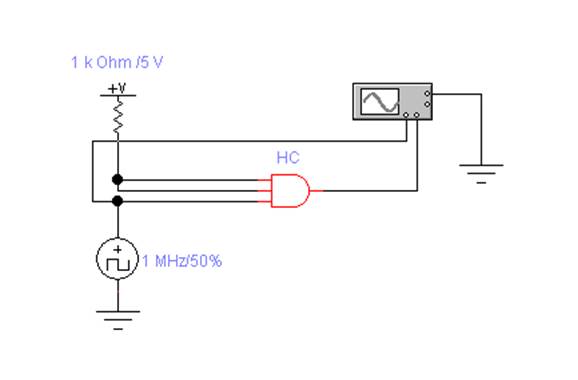

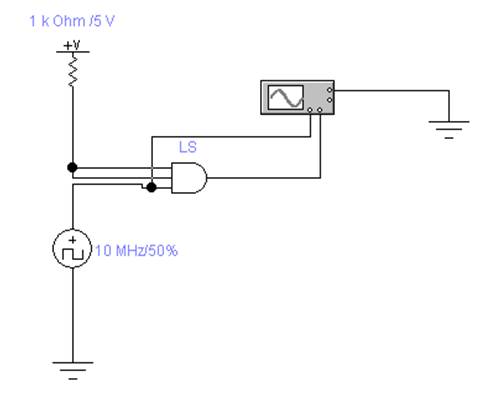

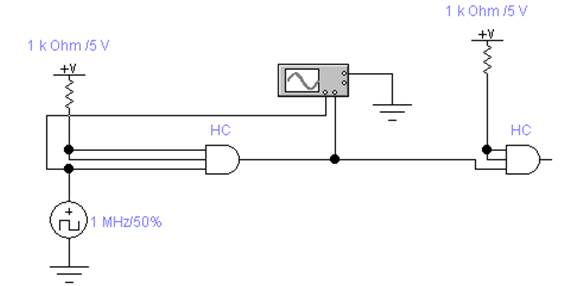

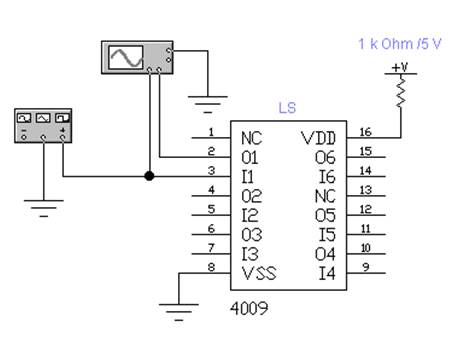

Время задержки (tpd) исследуется для 2-х типов микросхем: для КМОП-микросхемы и для ТТЛ-микросхемы в двух режимах – без нагрузки и с нагрузкой.

Собираем схемы для режима без нагрузки, рисунки 2 и 3, и для режима с нагрузкой, рисунки 4 и 5.

Рисунок 2 – Схема исследования КМОП-микросхемы без нагрузки.

Рисунок 3 – Схема исследования ТТЛ-микросхемы без нагрузки.

Рисунок 4 – Схема исследования КМОП-микросхемы с нагрузкой.

Рисунок 5 – Схема исследования ТТЛ-микросхемы с нагрузкой.

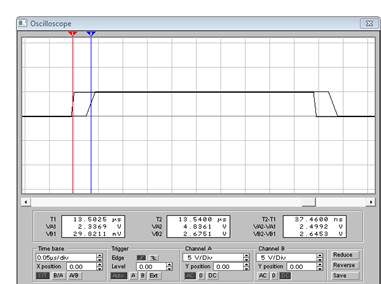

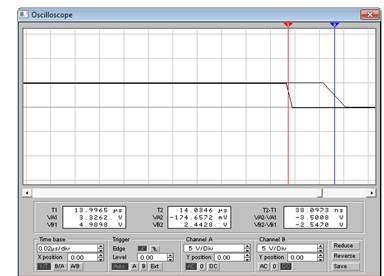

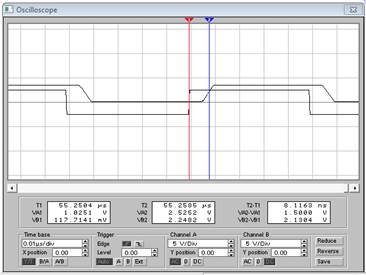

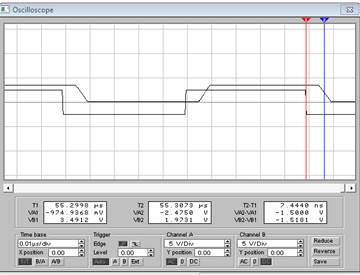

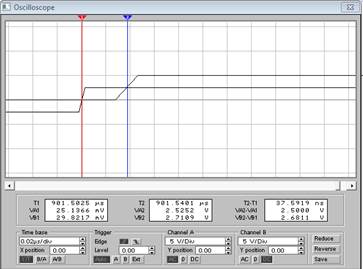

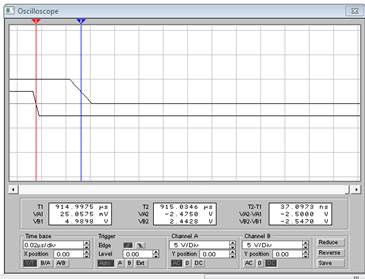

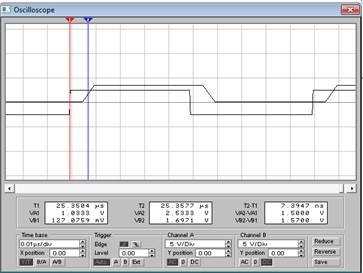

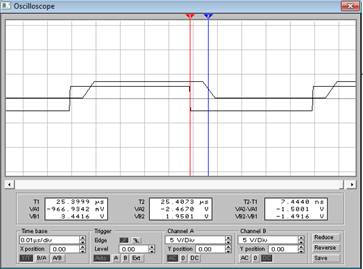

Измерение tPHL и tPLH для КМОП-микросхемы и ТТЛ-микросхемы представлены на рисунках 6, 7 и 8, 9 соответственно без нагрузки и 10,11 и 12, 13 с нагрузкой.

tPHL – время задержки при переходе выходного сигнала с высокого уровня на низкий.

tPLH - время задержки при переходе выходного сигнала с низкого уровня на высокий.

Рисунок 6 - Измерение tPHL для КМОП-микросхемы без нагрузки.

Рисунок 7 - Измерение tPLH для КМОП-микросхемы без нагрузки.

Рисунок 8 - Измерение tPHL для ТТЛ-микросхемы без нагрузки.

Рисунок 9 - Измерение tPLH для ТТЛ-микросхемы без нагрузки.

Рисунок 10 - Измерение tPHL для КМОП-микросхемы с нагрузкой.

Рисунок 11 - Измерение tPLH для КМОП-микросхемы с нагрузкой.

Рисунок 12 - Измерение tPHL для ТТЛ-микросхемы с нагрузкой.

Рисунок 13 - Измерение tPLH для ТТЛ-микросхемы с нагрузкой.

Таблица 2.

|

ИС |

Модель |

tpd, нс |

tpdнагр, нс |

UILпор, В |

UILmax, В |

UIHпор, В |

UIHmin, В |

DUIL, В |

DUIH, В |

|

ТТЛ |

LS |

7.6 |

7.4 |

0.6 |

2.4 |

||||

|

КМОП |

HC |

37 |

37.4 |

-------- |

--------- |

--------- |

---------- |

---------- |

---------- |

Рассчитать среднее времени задержки по формуле:

tpd = (tPHL + tPLH)/2

Результаты записать в таблицу 2.

2.3 Измерение пороговых уровней входных сигналов напряжения, соответ-ствующих логической «1» и «0» (VIH ,VIL). Расчет помехоустойчивости.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.