РАЗРАБОТКА АППАРАТНОЙ ЧАСТИ КОНТРОЛЛЕРА

Блок CPU

В контроллере диагностики канала передачи информации используется микропроцессор i8085 AH-2. Выбор именно такого микропроцессора обусловлен тем, что его тактовая частота, исходя из задания, должна быть равна 4 МГц. Такую частоту может обеспечить микропроцессор i8085 AH-2, способный работать с максимальной тактовой частотой 5 МГц. Частоту 4 МГц можно получить, подключив к входам Х1 и Х2 микропроцессора генератор с частотой 8 МГц. Вместе с данным микропроцессором используются микросхемы 8155Н2 (с помощью этой микросхемы выполнена память типа RAM, объемом 256 Byte) и 8755 ( на данной микросхеме выполнена память типа ROM, объемом 2 KByte). Выбор такой микросхемы для реализации RAM связан с использованием микропроцессора i8085 AH-2, а не i8085, благодаря этому она имеет полную совместимость при подключении и по уровню формируемых сигналов.

Блок памяти

Микросхема 8155H-2 имеет три порта ввода вывода и таймер. Таймер служит для формирования сигнала Fscan, который используется для загрузки данных индикации: загрузка производится по запросу прерывания сигналом Inter Fscan, который поступает на вход микропроцессора RST5.5.

Микросхема 8755 служит в качестве ROM. Порты ввода/вывода – не используются.

Прибор 8755 обладает невысоким быстродействием (время доступа прибора 8755Aравно 450 нс), поэтому может работать без сигналов READY только для микропроцессоров 8085AH. Указанный тип МП предназначен для работы на частотах до 3 МГц, более высокочастотные варианты МП должны использовать автомат готовности, имеющийся в приборе 8755. При подключении выходного сигнала этого автомата готовности к входу READY МП необходимо обратить внимание на его Z-состояние и добавить «подтягивающий» резистор, подключенный к Vcc. Подробнее автомат готовности описан в [3].

Блок приема пакетов управления на структурной схеме рис. 2.12 обозначен как УВВ1. Исходя из задания, блок должен быть реализован в виде двунаправленной схемы на прием пакета от ПК и вывода ответа после приема своего пакета управления и настройки контроллера. Ввод данных должен быть выполнен по прерыванию.

Структурная схема устройства программного ввода с квитированием приведена во второй дополненной версии [3, рис. 2.10], помещенной на компакт-диске.

Структурные схемы указывают на необходимые сигналы для ввода (внешняя шина данных DI[0,7], строб STB# и сигнал квитирования IBF) и вывода (строб OBF# и сигнал подтверждения ACK# и шина данных DO[0, 7]). Там же приведена принципиальная схема.

В соответствии с требованиями технического задания, для ввода/вывода используется параллельный канал на внешних регистрах. Ввод осуществляется с квитированием по опросу. В состав схемы параллельного ввода-вывода включены два регистра 1533ИР22 и 1533ИР23 (через них проходят данные), два триггера 1533ТМ2 (для формирования сигналов заполнения входного и выходного буферов IBF и OBF, для принятия стробовых сигналов и сигналов, разрешающих ввод/вывод I/OR и I/OW), а также драйвер 1533АП5. В качестве селектора адреса использован демультиплексор 555ИД7[3].

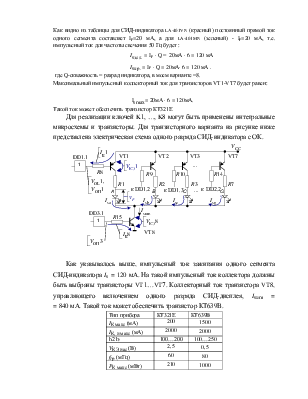

Блок Индикации

Блок индикации выполнен по стандартной динамической схеме, за счет чего используется минимальное число дополнительных микросхем. А использование прерываний позволяет максимально уменьшить затраты машинных ресурсов на процесс индикации. В качестве регистров используется используются порты А, В и С микросхемы 8155. Расчет элементов блока индикации приведен далее.

Исходя из того, что БИС индикация выбрана LA-401VN, LA-401MN, а микросхема 8155 имеет свободны порты A, B и С удобно использовать эти порты для подключения индикаторных устройств (используется 12 СИД дисплеев). Такое подключение позволяет не использовать дополнительных регистров и сократить число элементов контроллера. При этом задействованы семь пинов порта А, все восемь пинов порта B и четыре пина порта С (порты B и C служат для вывода строба разрешения высветки).

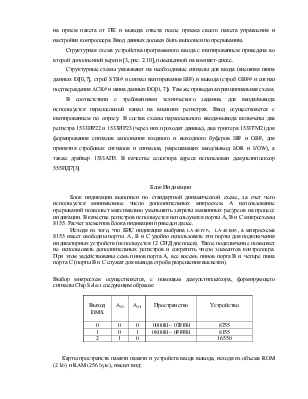

Выбор микросхем осуществляется, с помощью демультиплексора, формирующего сигналы Chip Select следующим образом:

|

Выход DMX |

A15 |

A14 |

Пространство |

Устройство |

|

0 |

0 |

0 |

0000H – 07FFH |

8755 |

|

1 |

0 |

1 |

0800H – 0FFFH |

8155 |

|

2 |

1 |

0 |

16550 |

Карты пространств памяти памяти и устройств ввода вывода, исходя из объема ROM (2 kb) и RAM (256 byte), имеют вид:

Карта пространства памяти

|

Модуль |

Адреса |

|

ROM |

0000H – 07FFH |

|

RAM |

0800H – 08FFH |

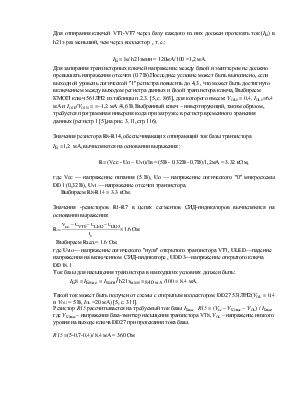

БИС приема управляющих пакетов выполнена, как последовательный канал ввода/вывода 16550. т.к представляет более современный вариант и обладает лучшими характеристиками.

При построении микроконтроллера применяются микросхемы ТТЛ серий, которые используются для реализации логических элементов «или».

В задании на курсовой расчет для построения индикаторного устройства рекомендуется использовать одноразрядные СИД-индикаторы с общим катодом (ОК)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.