преобразователи двоичного кода в код управления сегментными индикаторами;

• преобразователи двоичного или двоично-десятичного кода в код управления шкальными или матричными индикаторами.

Преобразователи кодов выпускают на ИМС К155ИД8, ИД10, ИД11, ИД12, ИД13, ИД15.

Примерами преобразователей кодов, которые широко применяют в цифровых устройствах, являются шифраторы и дешифраторы.

Шифратором называют кодовый преобразователь, который имеет n входов и К выходов, и при подаче сигнала на один из входов на выходах появляется двоичный код возбужденного входа.

В шифраторе n и К связаны соотношением n = 2К.

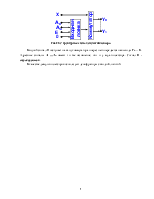

Рассмотрим принцип построения шифратора на примере преобразования 8-разрядного единичного кода в двоичный код (рис.15).

|

|

|

|

а) |

б) |

Рисунок 15. Схема шифратора восьмиразрядного единичного кода (а)

и его условное обозначение (б).

Если все входные сигналы имеют нулевое значение, то на выходе шифратора имеем нулевой код У0 = У1 = У2= 0.

Для шифровки кодов, отличных от нуля, воспользуемся таблицей соответствия кодов.

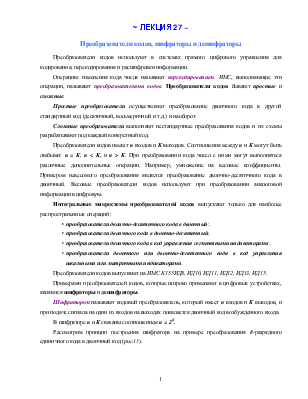

Соответствие 8-разрядного единичного кода двоичному представлено в таблице 1.

Таблица 1

|

Входы nx |

Выходы Ky |

||

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

Младший выход, т.е. выход с весовым коэффициентом равным 1, должен возбуждаться при наличии сигналов на любых нечетных водах, т.к. все нечетные номера в двоичном представлении содержат единицу в младшем разряде. Следовательно, младший выход – это выход схемы ИЛИ, к входам которой подключены все входы с нечетными номерами.

Следующий выход имеет вес два. Он должен возбуждаться при подаче сигналов на входы с номерами 2, 3, 6, 7, т.е. имеющими в двоичном представлении единицу во втором разряде. Входы элемента ИЛИ должны быть подключены к входным сигналам, имеющим указанные номера.

Старший разряд двоичного кода формируется из входных сигналов с номерами 4, 5, 6 и 7 т.е. из четырех старших разрядов единичного кода.

Использование шифратора позволяет сжать информацию для передачи ее по меньшему числу линий связи, т.к. К < n.

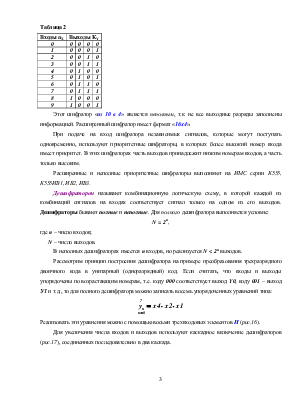

Например, в кнопочных пультах управления ввод числовых данных выполняется в десятичном коде нажатием одной из десяти кнопок. Для преобразования кода пульта в двоичный код процессора используют шифратор из 10 в 4 (см.табл.2).

Таблица 2

|

Входы nX |

Выходы КY |

|||

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

Этот шифратор «из 10 в 4» является неполным, т.к. не все выходные разряды заполнены информацией. Расширенный шифратор имеет формат «16х4».

При подаче на вход шифратора независимых сигналов, которые могут поступать одновременно, используют приоритетные шифраторы, в которых более высокий номер входа имеет приоритет. В этих шифраторах часть выходов принадлежит низким номерам входов, а часть только высоким.

Расширенные и неполные приоритетные шифраторы выполняют на ИМС серии К555, К555ИВ1, ИВ2, ИВ3.

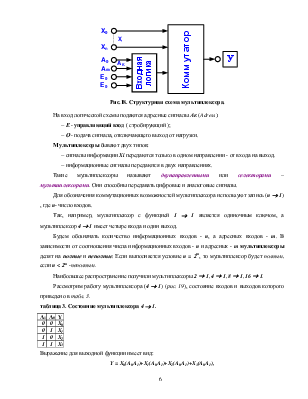

Дешифратором называют комбинационную логическую схему, в которой каждой из комбинаций сигналов на входах соответствует сигнал только на одном из его выходов. Дешифраторы бывают полные и неполные. Для полного дешифратора выполняется условие:

N = 2n,

где n – число входов;

N – число выходов.

В неполных дешифраторах имеется n входов, но реализуется N < 2n выходов.

Рассмотрим принцип построения дешифратора на примере преобразования трехразрядного двоичного кода в унитарный (одноразрядный) код. Если считать, что входы и выходы упорядочены по возрастающим номерам, т.е. коду 000 соответствует выход Y0, коду 001 – выход У1 и т.д., то для полного дешифратора можно записать восемь упорядоченных уравнений типа:

Реализовать эти уравнения можно с помощью восьми трехвходовых элементов И (рис.16).

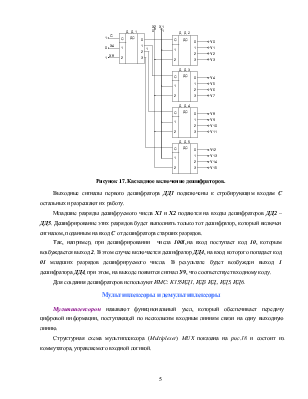

Для увеличения числа входов и выходов используют каскадное включение дешифраторов (рис.17), соединенных последовательно в два каскада.

|

|

|

Рисунок 16. Схема дешифратора 3х8 (а) и его условное изображение (б).

Кроме кодовых входов, каждый дешифратор имеет вход стробирующего сигнала (вход С). Сигнал на выходе дешифратора появляется только при С = 1.

На входы первого дешифратора подаются старшие разряды Х8 и Х4 числа

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.