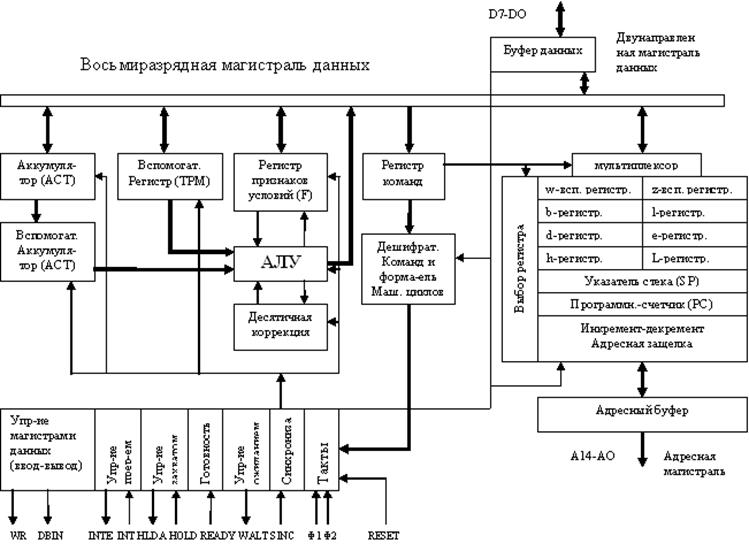

Регистры играют либо роль аккумуляторов, когда в них содержатся обрабатываемые данные, либо роль указателей, когда в них хранятся адреса операторов. Восьмиразрядные данные могут передаваться на внутреннюю шину данных МП через мультиплексор. Шестнадцати-разрядные адреса обмениваются между регистрами и буфером адреса через адресную защелку и схему инкремента – декремента адреса.

Структурная схема ЦПЭ типа К580 ИК80

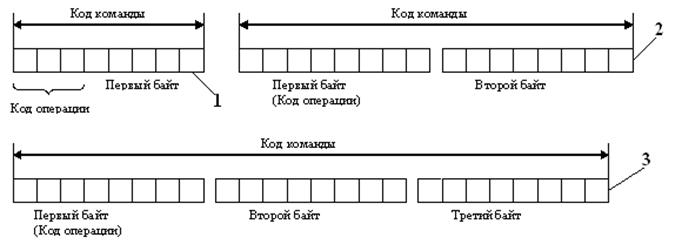

Система команд МП содержит команды различной длины в 1,2 и 3 байта информации (см. рис.).

Первый байт команды всегда помещается в регистр команд (РК). Второй и третий байты многобайтовых команд обычно размещаются во вспомогательных регистрах W и Z. Выбор того или иного регистра, участвующего в выполнении команды, производится схемой выбора регистров дешифрующей код команды, находящейся в РК.

Регистр команд. Первый байт команды, поступающей в РК, содержит код операции (см. рис.). Этот код расшифровывается дешифратором команд, который генерирует соответствующие микропрограммы формирования машинных циклов. Вся информация, определяющая последовательность выполнения команды, содержится в ее первом байте и размещается в виде кода операции в РК. Все дальнейшие действия по выполнению команды производятся в соответствии с микропрограммой через схему управления. Эта схема инициирует не только сигналы управления внутренними узлами МП, но и внешние сигналы, управляющие взаимодействием ЦП с памятью и устройствами “Вв.-выв”.

Буфер данных. Это двунаправленная схема с тремя логическими состояниями, предназначенная для обмена информацией МП с памятью и ВУ. Он изолирует МП от внешней магистрали данных, обеспечивая прямой доступ к памяти со стороны В.У. Если внутренняя магистраль данных находится в режиме ввода, о чем свидетельствует 1-ое значение сигнала DBIN. то буфер данных подключает внешнюю магистраль на ввод. Если, наоборот, на внутренней магистрали присутствуют данные для передачи из МП, о чем свидетельствует сигнал WR, равный нулю, то буфер данных подключает МП на вывод данных во внешнюю магистраль.

В отличие от двунаправленной магистрали данных, адресная шестнадцатиразрядная магистраль является однонаправленной и всегда работает только в режиме выдачи. Буферы обмена имеют выходные формирователи с тремя логическими состояниями, обеспечивающими отключение МП от адресной магистрали в режиме захвата этой магистрали другими МП или В.У.

Арифметико-логическое устройство. В МП оно занимает центральное место и представляет собой 8-ми разрядное параллельное устройство, обеспечивающее выполнение всех основных операций по обработке данных. Посредством устройства десятичной коррекции АЛУ может обрабатывать не только двоичные данные, но и двоично-десятичные коды (две десятичные цифры на одно слово). В обработке данных принимают участие следующие регистры: 8-разрядный аккумулятор (АСС); 8-разрядный вспомогательный аккумулятор (АСТ); 5-разрядный регистр признаков условий (F); 8-разрядный вспомогательный регистр временного хранения данных (ТРМ).

Регистр признаков условий служит для индикации состояния результата операции и включает в себя пять триггеров условий:

Z – триггер нулевого результата; СY – триггер переноса из старшего разряда; S – триггер знака; Р- триггер четности результата; С/ (или АС) – триггер вспомогательного переноса из третьего разряда.

Распределение разрядов регистра признака условий при передаче по шине данных следующее:

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

Dо |

|

S |

Z |

0 |

C/ |

0 |

P |

1 |

CY |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.