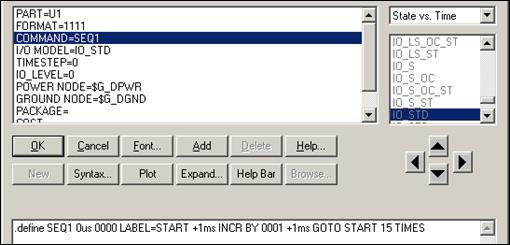

На условном обозначении генератора старший разряд отмечен точкой. Соответственно, с этого вывода снимается сигнал x3, т.е. старший разряд набора x3x2x1x0.

Чтобы при анализе работы схемы не следить постоянно за изменениями номеров узлов при добавлении или удалении элементов, удобно задать имена входным и выходным сигналам. Для этого необходимо перейти в режим Text Mode (кнопка T на панели инструментов), навести курсор на желаемый проводник на схеме и нажать левую кнопку мыши. В появившемся окне Grid Text на закладке Text ввести имя сигнала.

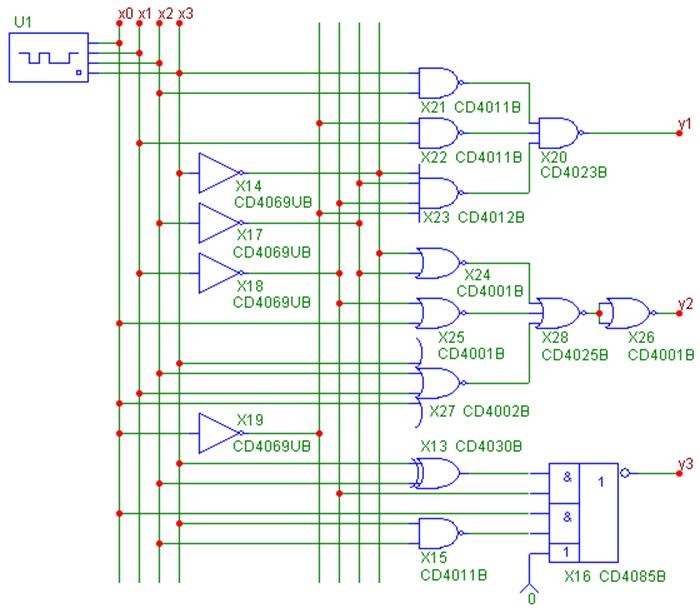

Ниже на рисунке приведён пример собранной схемы. В этом примере функция истинна на следующих наборах: {0, 2, 6, 10, 12, 13, 14, 15}; схема построена на ИМС КМОП серии 4000. Схема в базисе И‑НЕ выдаёт сигнал y1, схема в базисе ИЛИ-НЕ — y2, схема, реализованная с использованием минимального числа элементов — y3. Генератор формирует сигналы x0, x1, x2, x3, организованные в виде четырёх шин. При помощи четырёх инверторов из них формируются шины инверсных сигналов.

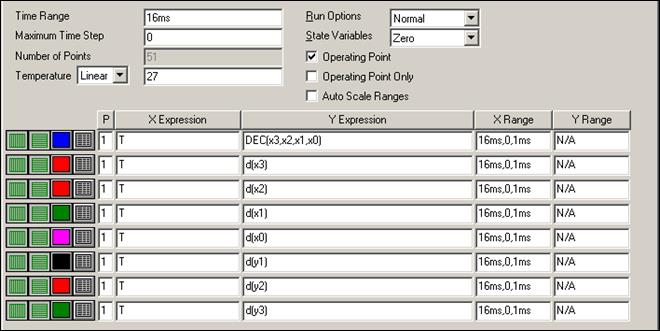

После того, как схема полностью собрана, необходимо построить временные диаграммы её работы, т.е. графики изменения во времени всех входных и выходных сигналов. Временные диаграммы строятся в режиме анализа переходных процессов (Transient Analysis). При этом если параметры генератора тестовых сигналов заданы так, как было рекомендовано ранее, то параметры режима Transient Analysis удобно задать так, как показано на рисунке ниже.

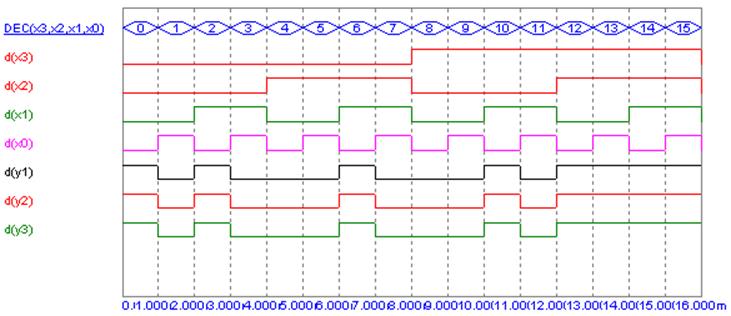

В этом примере входным сигналам присвоены имена x3, x2,x1, x0, выходным — y1, y2, y3. При этом удобно в строку, задающую первый график, вписать выражение DEC(x3,x2,x1,x0). В этом случае первый «график» на временной диаграмме будет показывать номера наборов в десятичной системе. Следующие четыре графика покажут логические уровни входных переменных, а последние три — выходных. Получаемые графики приведены на следующем рисунке.

1. Титульный лист.

2. Номер варианта, задание.

3. Таблица истинности функции.

4. Карта

(карты) Карно и МДНФ для ![]() , МДНФ для

, МДНФ для ![]() , МКНФ для

, МКНФ для ![]() , МКНФ

для

, МКНФ

для ![]() .

.

5. Приведение

![]() и

и ![]() к

базису И‑НЕ и составленная логическая схема.

к

базису И‑НЕ и составленная логическая схема.

6. Приведение

![]() и

и ![]() к

базису ИЛИ‑НЕ и составленная логическая схема.

к

базису ИЛИ‑НЕ и составленная логическая схема.

7. Преобразование функции и логическая схема, полученная при выполнении пункта 6 задания.

8. Чертёж собранной схемы в программе Micro-Cap.

9. Временные диаграммы работы схемы.

Вариант |

Номера наборов, на которых y=1 |

Элементная база |

|

1 |

0, 3, 4, 5, 6, 7, 10, 11, 12, 13 |

ТТЛ |

|

2 |

0, 4, 5, 7, 9, 10, 11, 12, 14 |

КМОП (серия 4000) |

|

3 |

2, 4, 6, 12, 13 |

КМОП (серия 74HC) |

|

4 |

1, 3, 4, 7, 8, 11, 12, 14 |

ТТЛ |

|

5 |

2, 4, 10, 12, 13, 14 |

КМОП (серия 4000) |

|

6 |

1, 2, 3, 4, 5, 6, 7, 9, 11, 12, 13, 14 |

КМОП (серия 74HC) |

|

7 |

0, 2, 3, 4, 5, 6, 7, 8, 13 |

ТТЛ |

|

8 |

0, 5, 8, 9, 14 |

КМОП (серия 4000) |

|

9 |

0, 2, 4, 5, 10, 14 |

КМОП (серия 74HC) |

|

10 |

6, 9, 10, 11, 14 |

ТТЛ |

|

11 |

2, 3, 5, 6, 7, 10, 12, 13, 14 |

КМОП (серия 4000) |

|

12 |

0, 1, 2, 3, 5, 7, 9, 10, 11, 12, 14 |

КМОП (серия 74HC) |

|

13 |

0, 2, 4, 6, 7, 9, 11, 12, 14 |

ТТЛ |

|

14 |

1, 3, 5, 13 |

КМОП (серия 4000) |

|

15 |

0, 1, 2, 3, 4, 10, 12, 13, 14 |

КМОП (серия 74HC) |

|

16 |

1, 2, 3, 4, 6, 7, 8, 9, 10, 11, 13, 14 |

ТТЛ |

|

17 |

0, 1, 2, 3, 5, 6, 8, 9, 10, 11, 13, 14 |

КМОП (серия 4000) |

|

18 |

6, 8, 9, 10, 14 |

КМОП (серия 74HC) |

|

19 |

0, 1, 2, 4, 7, 8, 9, 10, 11, 12, 13, 14 |

ТТЛ |

|

20 |

0, 1, 3, 4, 5, 6, 8, 9, 10, 11, 12, 13, 14 |

КМОП (серия 4000) |

|

21 |

1, 2, 4, 5, 8, 10, 11, 14 |

КМОП (серия 74HC) |

|

22 |

1, 2, 5, 9, 11, 12 |

ТТЛ |

|

23 |

2, 5, 8, 10 |

КМОП (серия 4000) |

|

24 |

0, 2, 6, 7, 8, 10, 12 |

КМОП (серия 74HC) |

|

25 |

2, 3, 5, 12, 13, 14 |

ТТЛ |

|

26 |

0, 1, 3, 4, 5, 6, 8, 9, 10, 11, 13, 14 |

КМОП (серия 4000) |

|

27 |

1, 2, 4, 5, 7, 8, 9, 10, 11 |

КМОП (серия 74HC) |

|

28 |

1, 2, 3, 4, 5, 6, 8, 9, 10, 11, 12 |

ТТЛ |

|

29 |

0, 2, 5, 7 |

КМОП (серия 4000) |

|

30 |

1, 3, 4, 6, 8, 11, 12, 14 |

КМОП (серия 74HC) |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.