Моделювання пристрою

Моделювання дільника частоти

Моделювання пристрою здійснювалося з викоританням пакета прикладних програм “Electronics Workbench” 4.0 (EWB 4.0). Була продемонстрована робота основних блоків пристрою – D тригера і логічного елементу 7І-НІ.

Тактові синхроімпульси на С-вхід тригера подавалися від зовнішнього генератора, що мається в бібліотеці приладів пакету EWB 4.0.

Тригери і логічні елементи, необхідні для побудови дільникка, були взяті з відповідних бібліотек елементів паакету EWB 4.0. У зв’язку з тим, що моделювання здійснювалося на основі функціональних схем, розроблених у розд. 1.2, бібліотеки інтегральних мікросхем пакету EWB 4.0 не використовувалися.

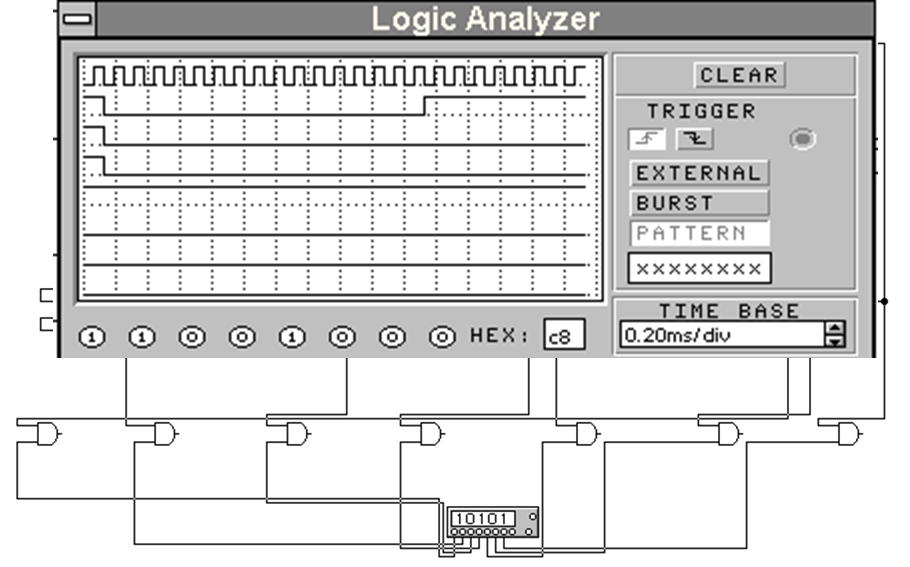

Контроль необхідних сигналів відповідно до тимчасової діаграми, розробленої в розділі 1.3, здійснювався за допомогою восьмиканального логічного аналізатора з бібліотеки приладів пакету EWB 4.0.

Результати, отримані в процесі роботи на логічному аналізаторі збігаються з результатами, представленими на тимчасовій діаграмі роботи дільника й окремих його блоків.

Cхема, яка була промодульована, представлена на рис. 4.1.

Рис. 4.1. Схема дільника

частоти.

При роботі в пакеті була отримана часова діаграма, що приведена на Рис. 4.2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.