Лабораторная работа № 5

Изучение сумматоров, цифрового компаратора и схемы контроля четности

Цель работы: изучение полусумматора, двухразрядного сумматора, компаратора и схемы контроля четности, проверка таблиц истинности.

Используемое оборудование:

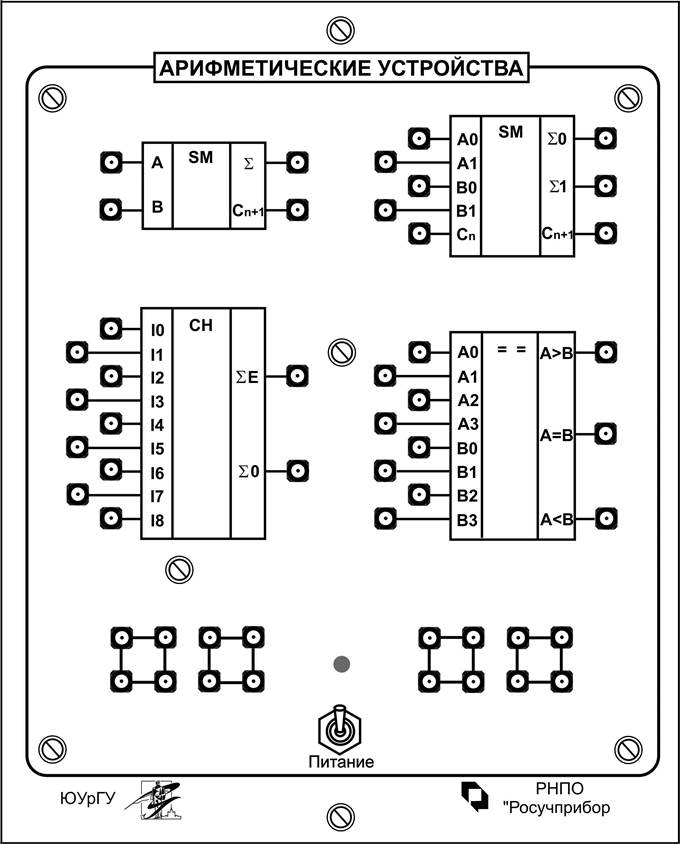

· лабораторный модуль «Арифметические устройства» (Рисунок 5.1);

· лабораторный модуль «Задание сигналов и логические элементы»;

· «Модуль питания и измерений»;

· соединительные проводники.

Рис. 5.1. Внешний вид передней панели «Арифметические устройства»

Порядок выполнения лабораторной работы

1. Изучить теоретический материал достаточный для выполнения лабораторной работы.

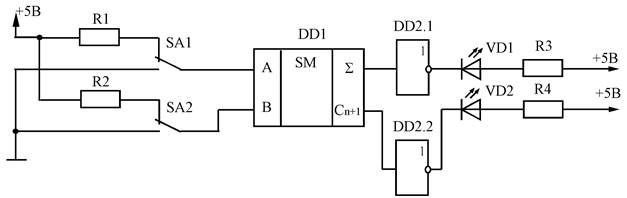

2. Собрать схему лабораторного стенда для изучения арифметических устройств (Рисунок 5.2), предварительно составив электрическую схему соединений лабораторного стенда на черновике и показав ее преподавателю или лаборанту. При выполнении лабораторной необходимо входы микросхемы соединить посредством соединительных проводников с источником логических сигналов (ключи SA). После проверки правильности схемы соединений преподавателем или лаборантом – подать напряжение питания 5В на стенд, включением тумблера питания.

Рисунок 5.2 –– Схема электрическая принципиальная лабораторного стенда для исследования полусумматора

3. Снять и зафиксировать на черновике таблицы истинности исследуемых устройств. По справочным таблицам истинности проверить правильность работы исследуемой схемы.

3.1. Изучение арифметического устройства –– полусумматор.

3.1.1. Собрать схему для исследования работы устройства (Рисунок 5.2). При проведении лабораторной работы необходимо подать при помощи соединительных проводников сигналы с гнезд «Уровень логический» (ключи SA), задавая различные комбинации входных логических сигналов, выходной сигнал контролируется светодиодом на выходе инвертора модуля «Задание сигналов и логические элементы».

3.1.2. Результаты исследования занести в таблицу 5.1.

Таблица 5.1

|

Входы |

Выходы |

||

|

A |

B |

Сумма, Σ |

Перенос, Cn+1 |

3.2. Изучение арифметического –– двухразрядный сумматор.

3.2.1. Выполнять аналогично п. 3.1.1.

3.2.2. Результаты исследования занести в таблицу 5.2 (таблица приведена не полностью).

Таблица 5.2

|

Входы |

Выходы |

||||||

|

Cn |

A0 |

B0 |

A1 |

B1 |

Сумма, Σ |

Перенос, Cn+1 |

Десятичная форма |

3.3. Изучение арифметического –– цифровой компаратор.

3.3.1. Выполнять аналогично п. 3.1.1.

3.3.2. Результаты исследования занести в таблицу 5.3.

Таблица 5.3

|

Вариант |

Вход сравнения данных |

Выход |

|||||||||

|

A3 |

A2 |

A1 |

A0 |

B3 |

B2 |

B1 |

B0 |

A>B |

A<B |

A=B |

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|||

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

||||

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

||||

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

||||

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

||||

|

Вариант |

Вход сравнения данных |

Выход |

|||||||||

|

A3 |

A2 |

A1 |

A0 |

B3 |

B2 |

B1 |

B0 |

A>B |

A<B |

A=B |

|

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|||

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

||||

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

||||

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

||||

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||||

|

Вариант |

Вход сравнения данных |

Выход |

|||||||||

|

A3 |

A2 |

A1 |

A0 |

B3 |

B2 |

B1 |

B0 |

A>B |

A<B |

A=B |

|

|

3 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|||

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

||||

|

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

||||

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

||||

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

||||

|

Вариант |

Вход сравнения данных |

Выход |

|||||||||

|

A3 |

A2 |

A1 |

A0 |

B3 |

B2 |

B1 |

B0 |

A>B |

A<B |

A=B |

|

|

4 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|||

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

||||

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

||||

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||||

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

||||

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.