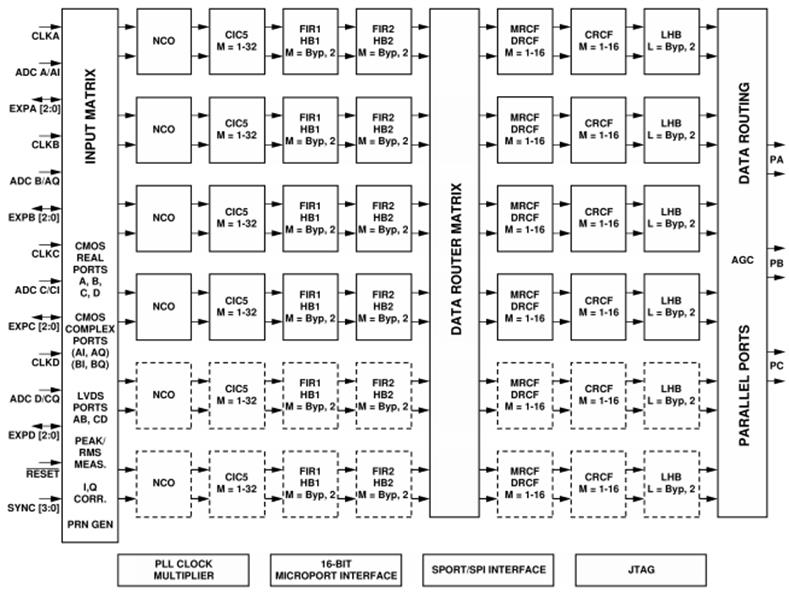

параллельный интерфейс ввода данных;

разрядность входных данных – с фиксированной точкой (16 бит) или с плавающей точкой (16 мантисса+3 экспонента);

встроенные цифровые гетеродины NCO с заданием частоты в виде 32-разрядного цифрового кода;

фильтры для осуществления децимации и фильтрации;

порты SPORT, SPI для связи с ЦП/МК;

SNR=101 дБ;

напряжение питания 3.3 В, 1.8 В;

максимальный ток потребления 500 мА.

Рис 6. Структура DDC AD6636

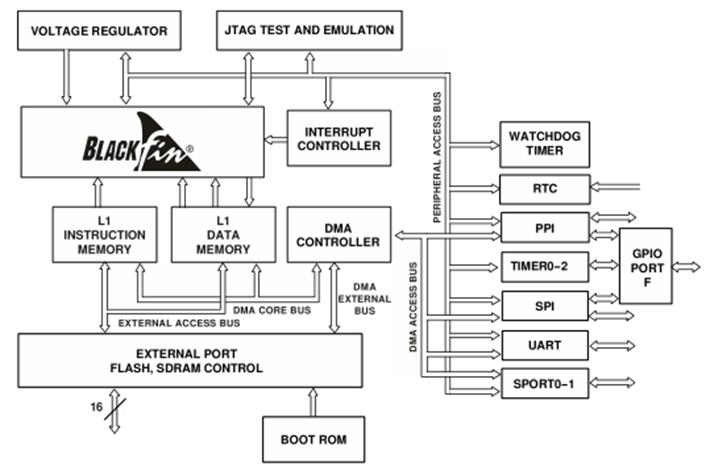

Для осуществления последующей цифровой обработки (селекции нужного канала, детектирования и т.д.) возьмем цифровой сигнальный процессор ADSP-BF533 – рис. 7. Он является высокопроизводительным решением фирмы Analog Devices семейства Blackfin. Основные характеристики данного процессора:

максимальная частота ядра 600 МГц;

два 16-битных перемножителя MAC, два 40-битных АЛУ;

до 146 КБ внутренней памяти;

параллельный интерфейс ввода/вывода, интерфейс SPI, SPORT, JTAG;

3 таймера/счетчика с ШИМ-режимом;

напряжение питания 3.3 В.

Рис 7. Структура ADSP-BF533

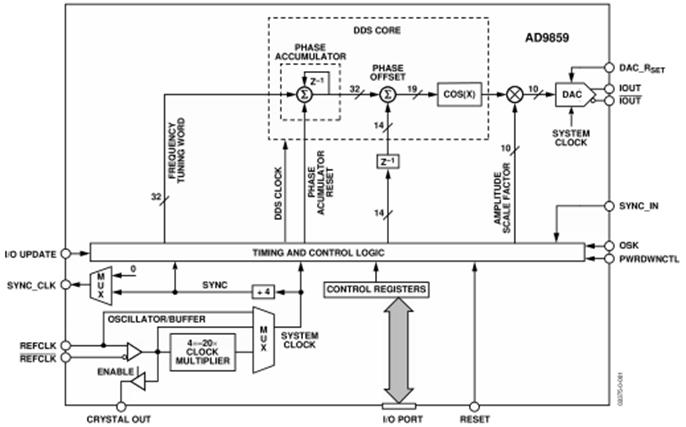

В качестве генератора напряжения частоты дискретизации целесообразно выбрать цифровой метод синтеза частоты. С учетом запаса частоты (примерно в 4-5 раз) возьмем микросхему DDS AD9859:

диапазон генерируемых частот – 1…400 МГц (без умножения частоты);

разрешение цифрового кода в ЦАП – 10 бит;

разрядность кода частоты – 32 бит;

SFDR на частоте 80 МГц – 87 dBc;

напряжение питания 1.8 В и 3.3 В.

Рис 8. Структура DDS AD9859

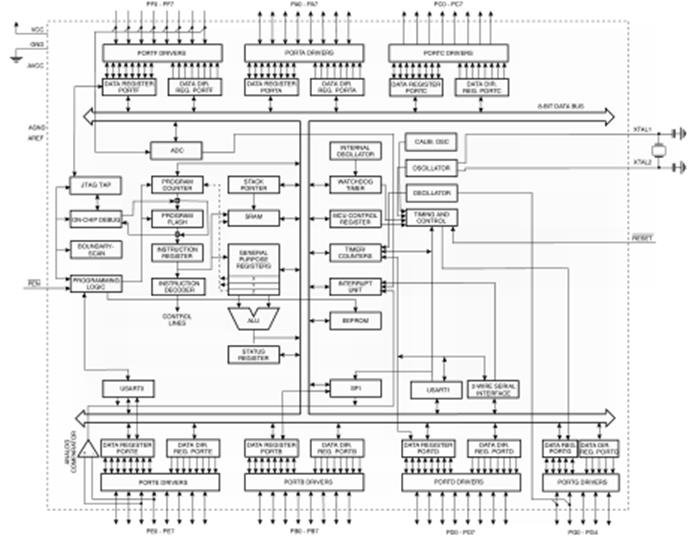

Для управления работой микросхем приемника возьмем микроконтроллер ATmega64-16Aw:

Flash память программ: 64 Кбайт;

Память данных: EEPROM 2 Kбайт, SRAM 4 Кбайт;

Количество линий ввода/вывода: 53;

Количество источников прерываний: 26 (внутренние), 8(внешние);

Интерфейсы: 1 SPI, 2 USART, 1 TWI;

Рабочая частота: 0…16 МГц;

Напряжение питания: 4.5…5.5 В.

Рис 9. Структура MC Atmega64

Управление синтезатором частоты AD9859 (запись кода частоты) организуем по последовательному порту SPI, управление AD6636 – по USART0, управление переключением аттенюаторов через порты микроконтроллера. Включение аттенюаторов выполним с использованием функции Control Gain. Смысл функции заключается в измерении мощности сигнала и превышении заданного порога – формирование сигнала управления через выводы EXP[2…0] на внешнюю схему – микроконтроллер, который в свою очередь управляет аттенюаторами. Кроме того, в качестве внешнего управления, например с компьютера, всего приемника возьмем COM-порт (RS-232) по протоколу RS-485, для чего использует транслятор уровней ADM488 и порт USART1 микроконтроллера.

Подсчитаем количество необходимых выводов управления:

8 выводов на аттенюаторы (инверсные биты формируются инверторами SN54ALS);

3 вывод на АЦП AD9244;

5 вывода на DDC AD6636;

3 вывода на DDS AD9859;

Заключение.

В ходе данной работы был разработан цифровой радиоприемник с супергетеродинным преобразованием частоты. Был произведен расчет частотного плана и выбор промежуточной частоты. Энергетический план выявил требования к усилению аналоговой части и ее шумовым свойствам. Расчет динамического диапазона показал необходимость введения в схему автоматической регулировки усиления (АРУ). В результате был спроектирован радиоприемник, соответствующий требованиям технического задания (ТЗ) на современной элементной базе.

Список использованной литературы.

1. Цифровые радиоприемные устройства: Методические указания к лабораторным работам/РГРТУ; Сост. Ю.Н. Паршин. Рязань, 2004. 52 с.

2. Лекции по курсу «ЦРПрУ», лектор Ю.Н. Паршин

3. Chengdu AINFO Inc. Filter

http://www.ainfoinc.com/en/p_mwrf_filc.asp

4. LMX2531 - High Performance Frequency Synthesizer System with Integrated VCO

http://www.alldatasheet.com/datasheet-pdf/pdf/297057/NSC/LMX2531.html

5. ADE-12MH - Frequency Mixer - Mini-Circuits

http://www.alldatasheet.com/datasheet-pdf/pdf/235485/MINI/ADE-12MH.html?

6. MAX2640, MAX2641: 300MHz to 2500MHz SiGe Ultra-Low-Noise Amplifiers

http://www.maximintegrated.com/datasheet/index.mvp/id/1918

7. Intermediate frequency

http://en.wikipedia.org/wiki/Intermediate_frequency

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.