Приложение А.

1)

1)

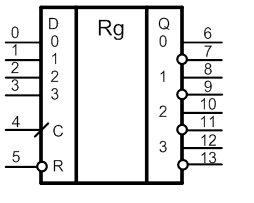

K555TM8

4х - разрядный регистр хранения информации, содержащий 4 синхронных D-триггера. Сброс происходит при подаче логического 0 на вход R, запись – по переходу импульса с отрицательной полярности на положительную на вход С. Информация на входах D1-D4 может меняться как при 0, так и при 1 на входе С, она важна лишь непосредственно перед изменением сигнала на входе С с 0 на 1.

|

Режим работы |

Вход |

Выход |

|||

|

R |

C |

Dn |

Qn |

не Qn |

|

|

сброс |

0 |

X |

X |

0 |

1 |

|

Загрузка 1 |

1 |

0-1 |

1 |

1 |

0 |

|

Загрузка 0 |

1 |

0-1 |

0 |

0 |

1 |

t0,1зд.рне более 28 нс;

t1,0зд.рне более 26 нс;

U1вых не менее 2,7 В

U0вых не более 0,5 В

I0вх не более -0,4 мА

I1вх не более 20 мкА

2)

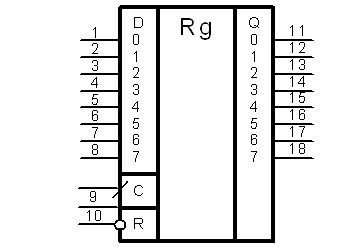

К555ИР35

8 - разрядный регистр c параллельной загрузкой и возможностью обнуления, при подаче низкого уровня на вход R. Ввод данных происходит по положительному фронту, приходящему на вход С.

t0,1зд.рне более 27 нс;

t1,0зд.рне более 20 нс;

U1вых не менее 2,4 В

U0вых не более 0,4 В

I0вх не более -0,2 мА

I1вх не более 20 мкА

Iпот не более 27 мА

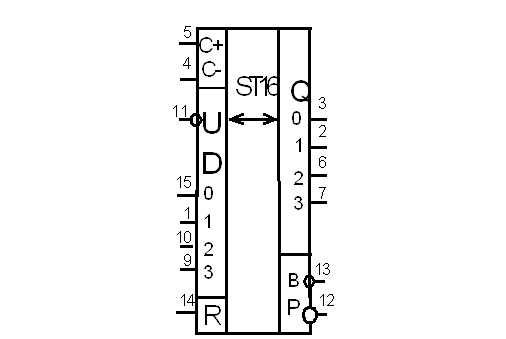

3)

К555

ИЕ7

К555

ИЕ7

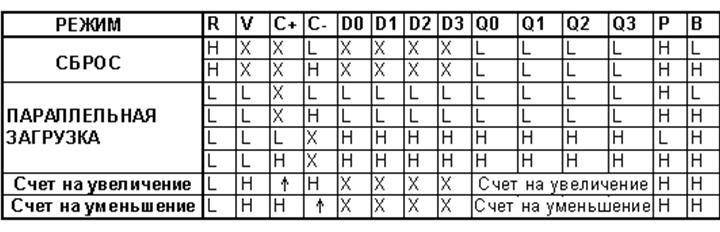

Двоичный реверсивный четырехразрядный счетчик, построенный на основе JK – триггеров.

Назначение выводов: 1, 9, 10, 15 – информационные входы; 2, 3,

6, 7 – выходы; 4, 5 – счетные входы; 8 – общий вход; 11 – вход разрешения

записи информации; 12 – выход переноса; 13 – выход заема; 14 – вход установки;

16 - ![]() .

.

Особенностью счетчика является его построение по синхронному принципу, по которому все триггеры схемы переключаются одновременно от одного счетного импульса. Направление счета в счетчике определяется состоянием на счетных входах триггера. При прямом счете на входе обратного счета должно быть напряжение высокого уровня, при обратном счете на входе прямого счета должно быть напряжение высокого уровня. Установка в ноль (сброс) счетчика осуществляется независимо от состояний информационных, счетных входов и входа предварительной записи. Для построения счетчика с большей разрядностью используются выходы прямого и обратного переноса. С выхода прямого переноса импульсы подаются на вход прямого счета следующего каскада. Импульсы обратного переноса подаются на вход обратного счета следующего каскада.

Таблица истинности

Iпот не более 33 мА U1вых не менее 2,7 В

I0вх не более -0,4 мА U0вых не более 0,5 В

I1вх не более 20 мкА t0,1зд.рне более 18 нс;

t1,0зд.рне более 16 нс

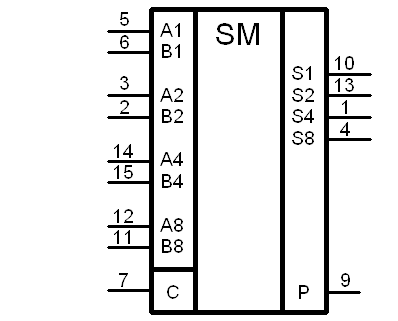

4) К555 ИМ6

Полный четырехразрядный двоичный сумматор.

На входы А1 - А8 подается код одного из суммируемых чисел (А1 - младший разряд, А8 - старший), на входы В1-В8 - код второго числа, на вход С - перенос от предыдущей микросхемы. Код суммы формируется на выходах S1 - S8, перенос - на выходе Р. У микросхемы, суммирующей младшие разряды многоразрядных двоичных чисел, вход С следует соединить с общим проводом.

Iпот не более 13 мА

I0вх не более -0,4 мА t1,0зд.рне более 21нс

U0вых не более 0,5 В U1вых не менее 2,7 В

I1вх не более 20 мкА t0,1зд.рне более20нс

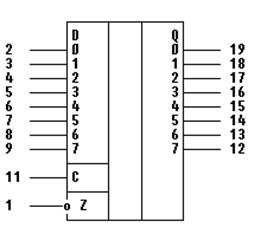

5) К555 ИР22

Восьмиразрядный

буферный регистр с защелкой и тремя состояниями.

Восьмиразрядный

буферный регистр с защелкой и тремя состояниями.

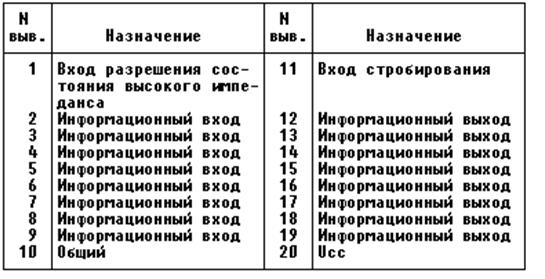

Назначение выводов:

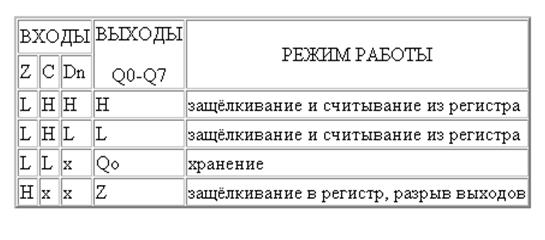

Базовый элемент микросхемы – D-триггер спроектирован по типу проходной защелки, что позволяет при высоком уровне на входе стробирования С проходить входному сигналу на выход минуя триггер. При подаче отрицательного уровня напряжения на вход С включается обратная связь и регистр запоминает поданную на вход D информацию и переходит в режим хранения. Высокий уровень на входе Z переводит выводы микросхемы в высокоимпедансное состояние, при этом в регистр может записываться новая информация или храниться предыдущая.

Таблица истинности:

Iпот не более 32 мА

I0вх не более -0,4 мА t1,0зд.рне более 26нс

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.