Количества входов и выходов полного дешифратора, т.е. дешифратора, использующего все комбинации двоичного кода, связаны соотношением: N=2m, где N – число выходов дешифратора; m – число двоичных входов.

Дешифраторы подобного типа строятся на комбинационных элементах.

В ЭВМ с помощью дешифратора осуществляется выборка необходимых ячеек запоминающих устройств, расшифровка кодов операций с выдачей соответствующих управляющих сигналов и т.д.

Состояние дешифратора, имеющего m=3 входа и 23=8 выходов, описывается табл.3, из которой следует, что каждому набору входных переменных x1, x2, x3 соответствует сигнал «1» только на одном выходе fi дешифратора.

Табл. 2

|

Входы |

Выходы |

|||||||||

|

x1 |

x2 |

x3 |

f0 |

f1 |

f2 |

f3 |

f4 |

f5 |

f6 |

F7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

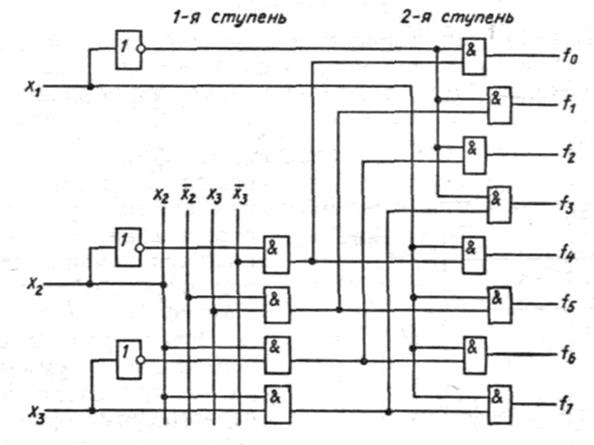

Функциональная схема и условие обозначение дешифратора приведены на рис.7, а, б соответственно.

Рис.7

Такой тип дешифратора по принципу действия является одноступенчатым (однокаскадным). Он обладает достаточно высоким быстродействием, однако при большом числе входов становится неэкономичным с точки зрения аппаратурных затрат.

Для дешифрации многоразрядных кодов используются многоступенчатые (каскадные) дешифраторы. На рис.8 в качестве примера показана схема двухступенчатого дешифратора на три входа, в которой в отличие от схемы, приведенной на рис.7, используются не трехвходовые, а более простые двухвходовые элеметы И.

Рис.8

По структурной организации различают линейные, пирамидальные и матричные дешифраторы.

Линейный дешифратор представляет собой группу из логических элементов И – НЕ, число которых равно числу выходов дешифратора, а число входов у каждого элемента равно числу входных переменных. Линейная структура дешифратора обеспечивает минимальную задержку прохождения сигнала, равную задержке одного вентиля. При такой структуре дешифратора с увеличением размерности кода существенно возрастает расход оборудования.

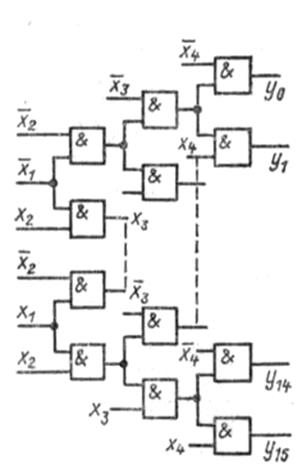

Пирамидальный дешифратор образуется при размещении в несколько ярусов ряда линейных дешифраторов, каждый из которых декодирует определённую группу переменных (рис.9). Ценой введения дополнительных задержек пирамидальная структура дешифратора по сравнению с линейной позволяет сократить расход оборудования и использовать логические элементы с небольшим количеством входов.

Рис.9

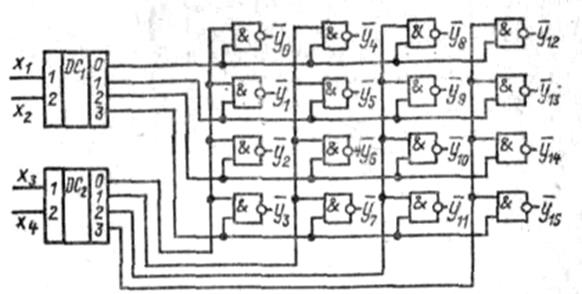

Матричными (или прямоугольными) называются такие схемы дешифраторов, в которых двухходовые логические элементы И – НЕ подключаются соответственно между вертикальными и горизонтальными шинами, на которые подаются разделённые на две части прямой и инверсный наборы входных переменных (рис.10).

Рис.10

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.