|

JK триггер |

|

LIBRARY ieee; USE ieee.std_logic_1164.all; entity JK_1 is port (C : in std_logic; J,K : in std_logic; R: in std_logic; Q,nQ: out std_logic); end JK_1; architecture rgr of JK_1 is signal state: std_logic; signal input: std_logic_vector(1 downto 0); begin input <= J & K; p: process(C, R) begin if (R='0') then state <= '0' after 9 ns; elsif (falling_edge(C)) then case (input) is when "11" => state <= not state; when "10" => state <= '1'; when "01" => state <= '0'; when others => null; end case; end if; end process; Q <= state after 16ns; NQ <= not state after 16ns; end rgr; |

|

|

||||

|

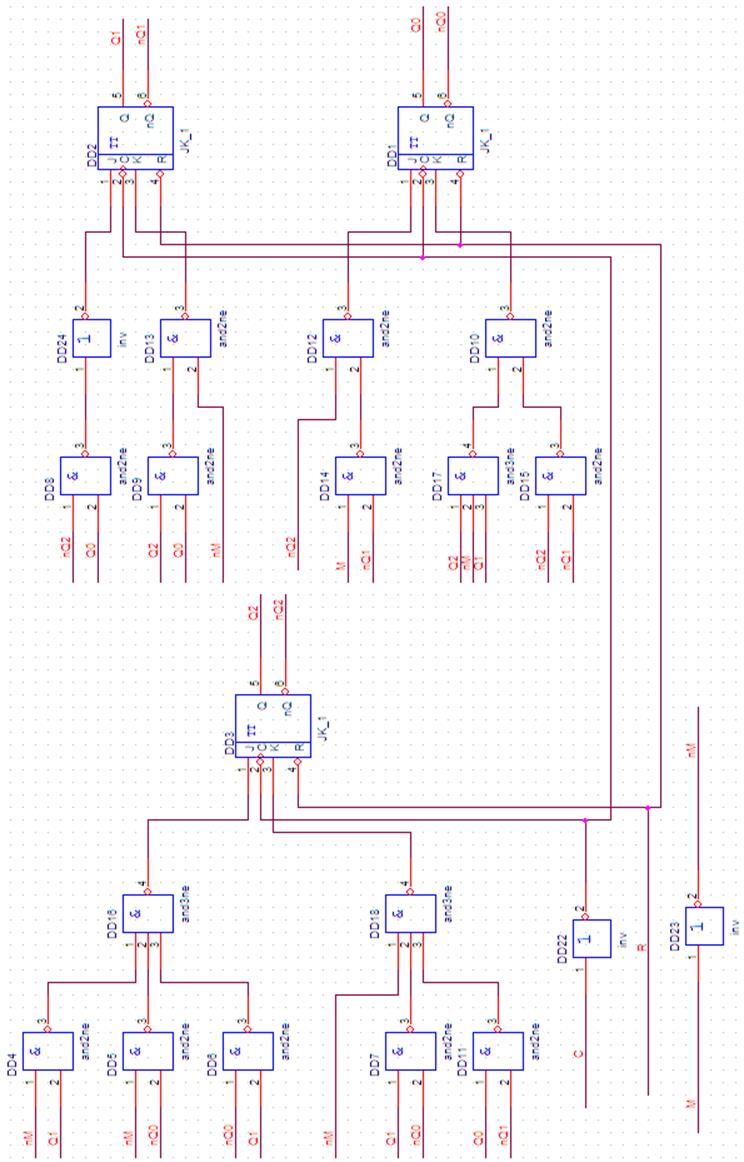

Рис. 10 – Иерархический блок, схема замещения которого реализует спроектированный автомат, построенный на абстрактных элементах с VHDL-описанием |

||||

|

|

||||

|

Рис. 12 – Результаты моделирования спроектированного автомата (рис. 10), построенного на абстрактных символах с VHDL-описанием |

||||

|

|

||||

|

Рис. 13 – Задержка распространения сигнала от входа сброса R до выходов Q при переключении выходов из состояния U в 0 |

||||

|

|

||||

|

Рис. 16 – Задержка распространения сигнала от входа C до выхода Q0 при переключении выхода Q0 из состояния 0 в 1 |

||||

|

Замечание. Задержки распространения сигнала от входа С до всех выходов Q совпадают. |

||||

5. Приложение

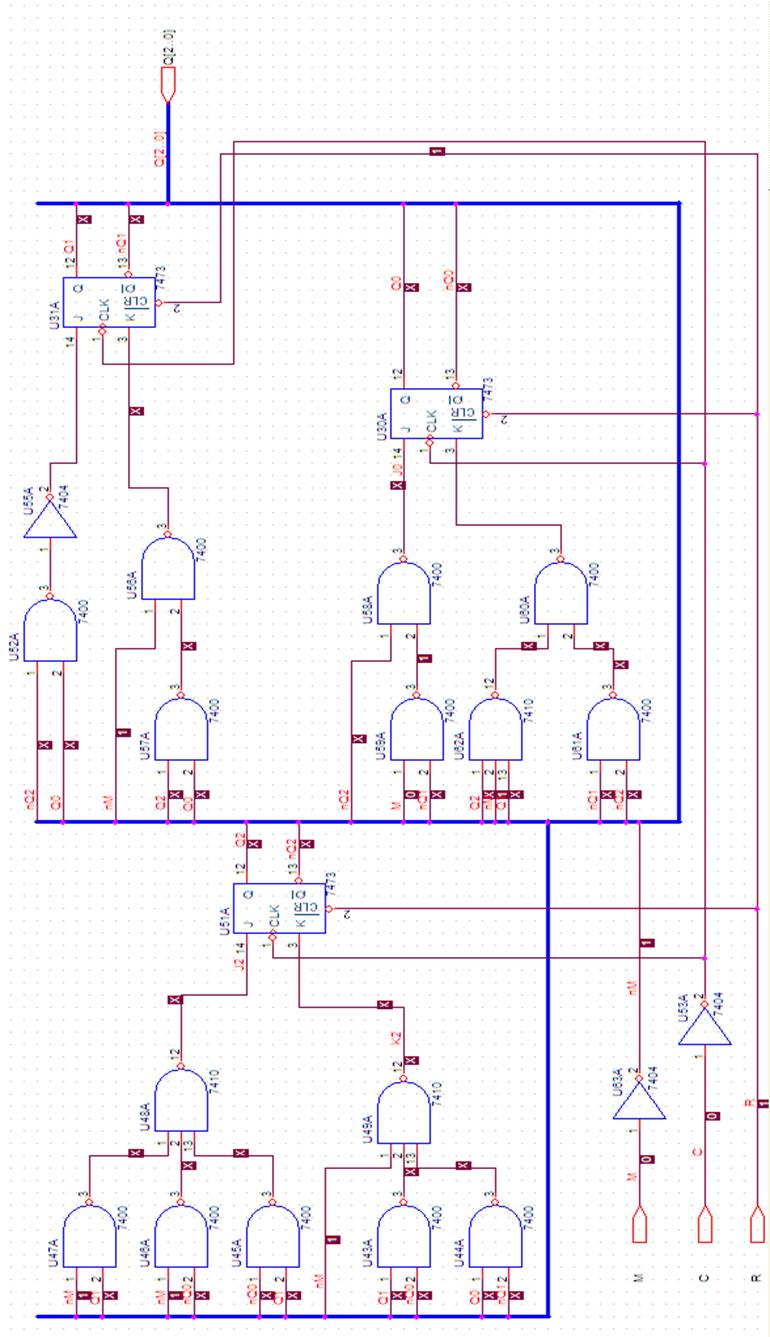

Рис. 17. Схема замещения на зарубежных компонентах.

Рис. 18. Схема замещения на иерархических символах.

В ходе выполнения расчётно-графической работы по дисциплине «Моделирование» были достигнуты следующие цели:

· Был изучен пакет САПР OrCAD 9.1.

· Освоены и отточены новые для меня методы проектирования, работа с иерархическими блоками, их схемами замещения и VHDL – моделями;

· Разобралась в принципах работы логических элементов, необходимость учитывать разницу между идеальными и реальными компонентами.

Хочу заметить некоторые удобства работы с данным пакетом:

· Удобный графический редактор, удобный пользовательский интерфейс;

· Имеет две поведенческих модели: внешняя – Pspice и внутренняя – VHDL, каждая из которых подходит для своих целей и нужд.

· Встроенный текстовый редактор – имеет различного рода заготовки, например VHDL Templateы очень помогли при написании VHDL – моделей.

· Редактор символов весьма удобен, интерфейс понятен и интуитивен, редактор содержит все необходимые инструменты для создания графического представления символа, улучшения его восприятия.

1. Шалагинов А.В. Журнал Компоненты и технологии. Знакомство с пакетом OrCad 9.1: 2002.

2. Угрюмов Е.П. «Цифровая схемотехника», 2001, BHV, Санкт – Петербург. Электронная версия.

3. Cправочник VHDL http://www.bsuir.by/vhdl/reference/

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.