|

31 23 |

22 0 |

|

КОП |

Адрес ветвления |

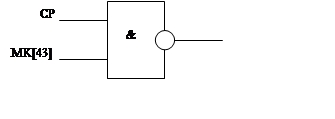

Данная команда используется для осуществления ветвления микропрограммы: в команду входят КОП и адрес ветвления (переход по такому адресу или переход, если какой-либо признак удовлетворяет условию).

4. Компоновка операционного блока (ОБ):

АЛУ Am29C332-2 и регистровый файл Am29C334 достаточно подробно описаны в источнике [1], поэтому разработчик не считает нужным приводить его в данной пояснительной записке.

В качестве регистров входных, выходных данных, адресного регистра используются по два 16-ти разрядных регистра фирмы IDT – IDT74FCT16374ET, так как шина данных и шина адреса 32-разные. Данные регистры имеют выходы с тремя состояниями, что обеспечивает возможность отключения их от локальной штны данных, это необходимо, так как кроме данных регистров на нее работают попеременно и другие источники, например память. Так как данные регистры фирмы IDT не имеют входа разрешения загрузки, адресный регистр тактируется синхросигналом и битом «тактирования адресного регистра» микрокоманды.

|

RGF: В ОБ используются две БИС RGF (организация 64x18 бит) для обеспечения заданной разрядности данных.

На входы Da0 – Da17 обеих секций данные передаются из регистра входных данных и из регистра команд. На входы Db0 – Db17 обеих секций данные передаются из локальной шины.

Адреса чтения/записи с шин Da/Db поступают через мультиплексор либо из регистра команд, либо из регистра микрокоманд. Управление мультиплексорами производится соответствующими битами микрокоманд по синхросигналу. Так как адреса записи/чтения берутся из одних полей микрокоманды, то они объединены и управляются совместно. Это сделано и для тракта А и для тракта В.

Тактирование входов #WEac, #WEbc осуществляется через мультиплексор синхросигналом и соответствующими битами микрокоманды. Так как минимальным элементом памяти, адресуемой процессором, является слово, входы разрешения записи первого и второго байта (#WEah и #WEal, #WEbh и #WEbl) объединены и на них подается логический «0».

Так как на входы данных ALU работает только RGF, и нет других устройств работающих параллельно, то входы #OEa и #OEb заземлены, то есть вывод данных в Ya – шину и Yb – шину регистрового файла всегда разрешен.

Входы разрешения защелки данных вывода портов вывода Ya и Yb управляются соответствующим разрядом микрокоманды.

ALU: Данные на входы Da/Db поступают с выходов Ya/Yb регистрового файла. Сигналы на входы P (задание правой границы обрабатываемого битового поля или задание параматра сдвига) и W (задание ширины битового поля) поступают через мультиплексор из регистра команд либо из регистра микрокоманд. Так как в ОБ используется только одно АЛУ, то используем АЛУ в режиме “ведущий” (SLAVE=L, MSERR=L). На входную штну C, Z, N, V ,L выбираем признаки с выходов АЛУ или из соответствующих разрядов SRG (RS управляется битом микрокоманды). Так как в данном проекте не предусмотрен контроль паритета для данных, то выход ошибки паритета, и входы паритета для операндов на шинах Da и Db, и выходы паритета для данных выводимых в Y – шину не используются (PRERR=L, PA0-3=L, PB0-3=L, PY0-3=L). За ненадобностью режима хранения статусного регистра – HOLD=L. Так как на Y – шину работает помимо АЛУ и MPL, то управление входом разрешения вывода данных в Y – шину (OEY#) производится соответствующим битом мкрокоманды. Входы I, P0-5, W0-4, MCin, MLINK, M/m# управляются соответствующими разрядами микрокоманды. АЛУ содержит встроенный 64-разрядный групповой сдвигатель и встроенный статусный регистр, работа которых описана в последующих пунктах пояснительной записки.

MPL: С целью сокращения длительности умножения в операции умножения задействованы внутренние регистры умножителя, поэтому операция умножения выполняется синхронно в два такта. Данные на вход умножителя поступают с внутренней шины, на нее они и выводятся после умножения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.