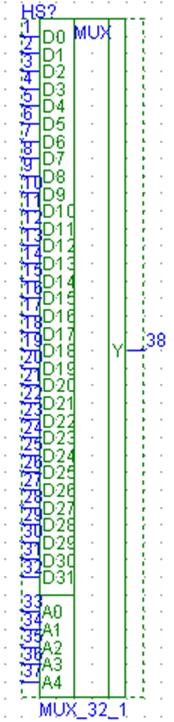

УГО мультиплексора 32->1 приведено на рисунке 10.

Текст DSL-модели приведен ниже:

PROCEDURE MUX32_1 (

INPUT D0, D1, D2, D3, D4, D5, D6, D7, D8, D9, D10, D11, D12, D13, D14, D15 ;

INPUT D16, D17, D18, D19, D20, D21, D22, D23, D24, D25, D26, D27 ;

INPUT D28, D29, D30, D31, A0, A1,

A2, A3, A4 ;

INPUT D28, D29, D30, D31, A0, A1,

A2, A3, A4 ;

OUTPUT Y ;

);

TRUTH_TABLE

A4,A3,A2,A1,A0 :: Y ;

"--------------------------------

0,0,0,0,0 :: D0 ;

0,0,0,0,1 :: D1 ;

0,0,0,1,0 :: D2 ;

0,0,0,1,1 :: D3 ;

0,0,1,0,0 :: D4 ;

0,0,1,0,1 :: D5 ;

0,0,1,1,0 :: D6 ;

0,0,1,1,1 :: D7 ;

0,1,0,0,0 :: D8 ;

0,1,0,0,1 :: D9 ;

0,1,0,1,0 :: D10 ;

0,1,0,1,1 :: D11 ;

0,1,1,0,0 :: D12;

0,1,1,0,1 :: D13 ;

0,1,1,1,0 :: D14 ;

0,1,1,1,1 :: D15;

1,0,0,0,0 :: D16;

1,0,0,0,1 :: D17;

1,0,0,1,0 :: D18;

1,0,0,1,1 :: D19;

1,0,1,0,0 :: D20;

1,0,1,0,1 :: D21;

1,0,1,1,0 :: D22;

1,0,1,1,1 :: D23;

1,1,0,0,0 :: D24;

1,1,0,0,1 :: D25;

1,1,0,1,0 :: D26;

1,1,0,1,1 :: D27;

1,1,1,0,0 :: D28;

1,1,1,0,1 :: D29;

1,1,1,1,0 :: D30;

1,1,1,1,1 :: D31; Рис.10

END TRUTH_TABLE;

END MUX32_1;

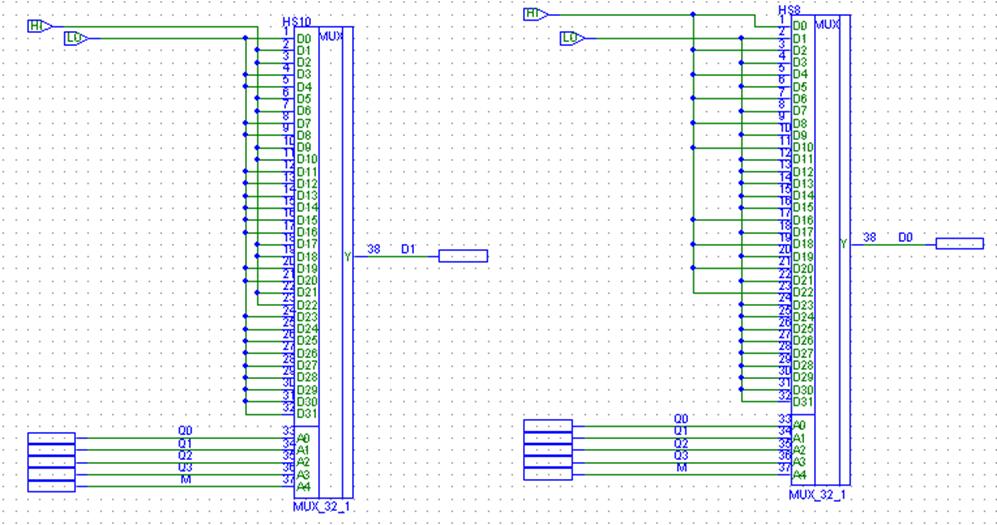

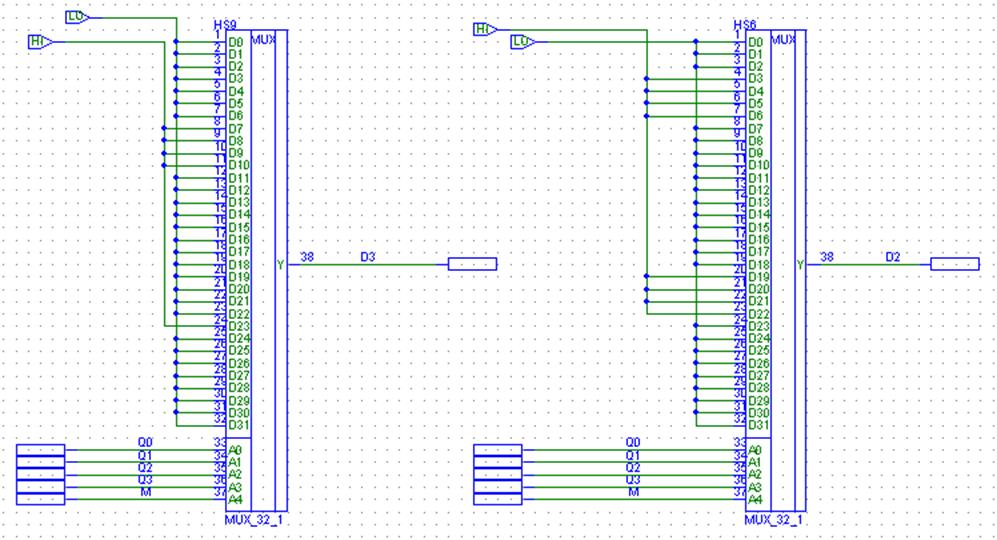

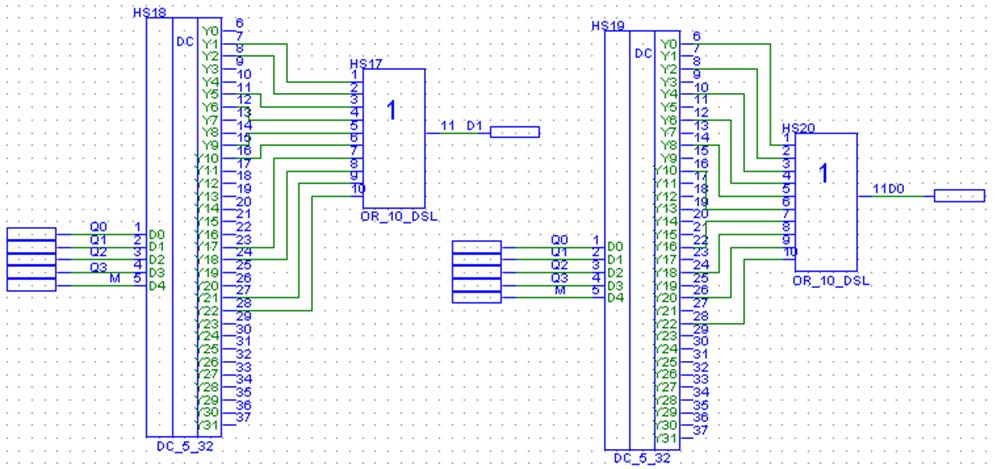

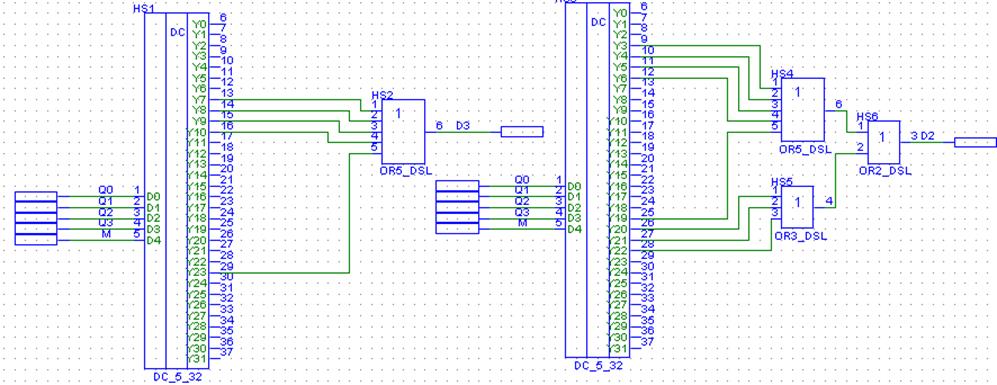

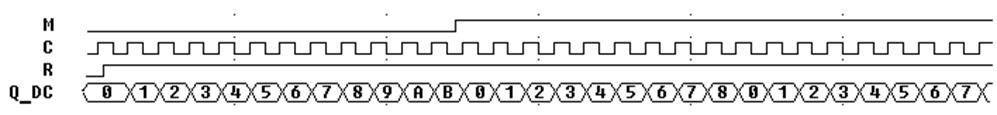

Схема реализации комбинационной части на мультиплексорах и результаты ее моделирования представлены на рисунках 11 и 12 соответственно.

Рис.11

Рис.12

Для реализации комбинационной части автомата на дешифраторах необходимо на их входы подавать значения аргументов функции возбуждения. Таким образом на выходах дешифратора мы получим набор всех возможных конъюнкций этих аргументов. Остается лишь объединить нужные конъюнкции по схеме ИЛИ и мы получим необходимую функцию возбуждения входа D-триггера.

Учитывая, что функция возбуждения зависит от 5 переменных необходимо спроектировать дешифратор 5->32, а также элемент 10-ИЛИ.

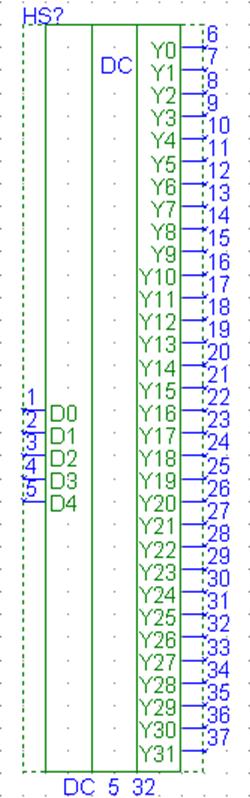

УГО дешифратора приведено на рисунке 13.

DSL-модель дешифратора 5->32:

PROCEDURE DC (

INPUT D0, D1, D2, D3, D4 ;

OUTPUT Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7, Y8, Y9, Y10, Y11, Y12, Y13, Y14, Y15 ;

OUTPUT Y16, Y17, Y18, Y19, Y20, Y21, Y22, Y23, Y24, Y25, Y26, Y27 ;

OUTPUT Y28, Y29, Y30, Y31 ;

);

);

TRUTH_TABLE

[D4..D0] :: [Y31..Y0];

0 :: 1;

1 :: 2;

2 :: 4;

3 :: 8;

4 :: 16;

5 :: 32;

6 :: 64;

7 :: 128;

8 :: 256;

9 :: 512;

10 :: 1024;

11 :: 2048;

12 :: 4096;

13 :: 8192;

14 :: 16384;

15 :: 32768;

16 :: 65536;

17 :: 131072;

18 :: 262144 ;

19 :: 524288 ;

20 :: 1048576;

21 :: 2097152;

22 :: 4194304;

23 :: 8388608;

24 :: 16777216;

25 :: 33554432;

26 :: 67108864;

27 :: 134217728 ;

28 :: 268435456;

29 :: 536870912 ;

30 :: 1073741824;

31 :: 2147483648 ;

END TRUTH_TABLE;

END DC;

Рис.13

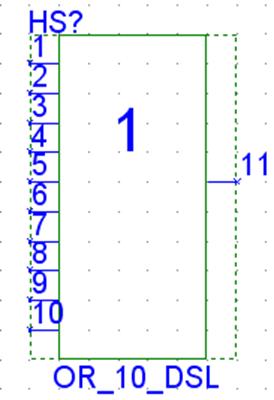

УГО логического элемента 10-ИЛИ приведено на рисунке 14.

DSL-модель логического элемента 10-ИЛИ:

PROCEDURE OR_10_DSL (

INPUT IN0, IN1, IN2, IN3,

IN4, IN5, IN6, IN7, IN8, IN9 ;

OUTPUT OUT ;

);

OUT=+(IN0..IN9);

END OR_10_DSL;

Рис.14

Схема реализации комбинационной части на дешифраторах и результаты ее моделирования представлены на рисунках 15 и 16 соответственно.

Рис.15

Рис.16

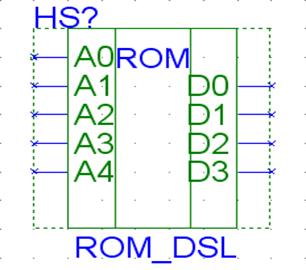

Для синтеза комбинационной части автомата на ПЗУ

достаточно просто зашить таблицы истинности функций возбуждения триггеров в

ПЗУ, подать на адресные входы ПЗУ переменные этих функций, а выходные данные

подать на соответствующие входы триггеров.

Для синтеза комбинационной части автомата на ПЗУ

достаточно просто зашить таблицы истинности функций возбуждения триггеров в

ПЗУ, подать на адресные входы ПЗУ переменные этих функций, а выходные данные

подать на соответствующие входы триггеров.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.