Дополнительная информация к лабораторной работе №1

Руководство по аппаратной части ADSP218x (в формате Adobe Acrobat) находятся в каталоге \Analog Devices\VisualDSP\Docs\218x_hwr. Содержание руководства находится в файле contents.pdf.

В программе аппроксимации синуса не используется алгоритм Горнера.

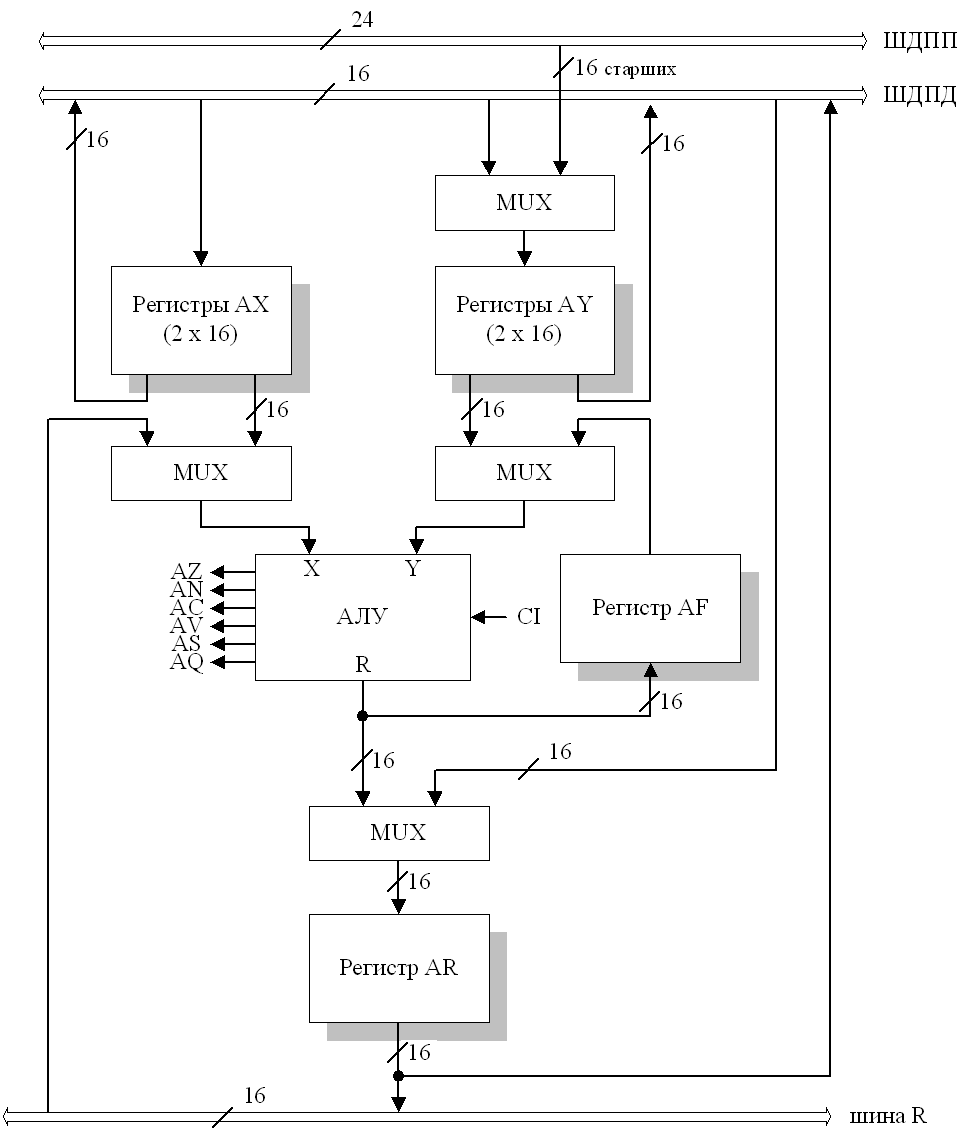

АЛУ имеет два 16-разрядных входных порта (X и Y) и один 16-разрядный выходной порт R. АЛУ принимает на вход один флаг переноса CI из арифметического статусного регистра процессора ASTAT и изменяет состояние шести флагов этого регистра: нулевого результата AZ, отрицательного результата AN, переноса AC, переполнения AV, знака входного операнда X AS и равенства AQ.

Входной порт X может получать данные из регистрового файла AX, или с шины результата R (т.е., с выхода любого из трех вычислительных устройств). Регистровый файл AX состоит из двух регистров AX0 и AX1. Оба этих регистра могут записываться и читаться через шину данных памяти данных. Система команд позволяет считывать эти регистры через шину данных памяти программ, однако, прямого выхода на шину памяти программ эти регистры не имеют и для их чтения через шину памяти программ используется блок обмена данными между шинами данных памяти программ и памяти данных. Выходы файла AX двухпортовые, что позволяет одновременно читать данные из одного регистра на вход АЛУ и на шину данных.

Входной порт Y также способен принимать данные от двух источников: из регистрового файла AY или от регистра AF обратной связи АЛУ. Регистровый файл AY состоит из двух регистров AY0 и AY1. Оба этих регистра могут записываться и читаться через шину данных памяти данных, а также записываться через шину данных памяти программ. Выходы файла AY также двухпортовые, что позволяет одновременно читать данные из одного регистра на вход АЛУ и на шину данных.

Код с выхода АЛУ может записываться в регистр обратной связи AF, регистр результата AR или отбрасываться.

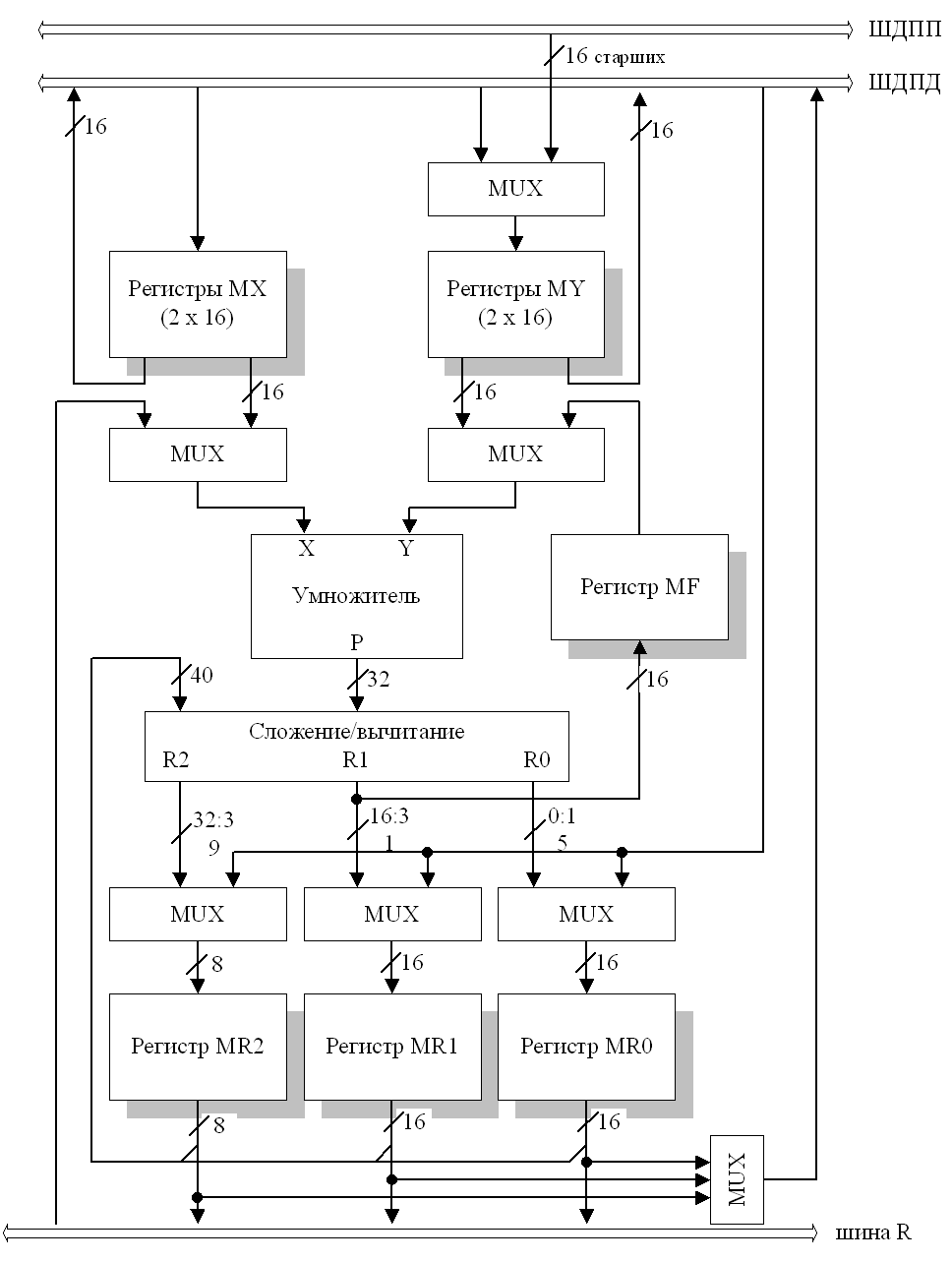

Умножитель имеет два 16-разрядных входных порта X и Y и 32-разрядный выходной порт произведения P. 32-разрядное произведение передается в 40-разрядное устройство сложения/вычитания, которое прибавляет или вычитает новое произведение к/из содержимому(ого) регистра результата MR. Также, произведение может напрямую передаваться в MR без сложения/вычитания. Регистр MR – 40-разрядный. Реально, он состоит из 3 меньших регистров: 16-разрядных MR0 и MR1 и 8-разрядного MR2.

Разрядность устройства сложения/вычитания выше 32 бит для того, чтобы сделать допустимыми промежуточные переполнения при последовательности операций умножения с накоплением. Бит статуса MV (Multiple Overflow) устанавливается при выходе результата в аккумуляторе за 32-битную границу (т.е., когда в старших 9 битах регистра MR присутствуют значащие (не путать со знаковыми) биты).

Входные и выходные регистры умножителя накопителя идентичны регистрам АЛУ. Входной порт X может получать данные из регистрового файла MX или из любого регистра результата по шине R. Регистровый файл содержит два регистра – MX0 и MX1. Эти регистры доступны на чтение и запись по шине данных памяти данных. Выход регистрового файла MX – двухпортовый, что позволяет одновременно считывать содержимое одного из регистров через шину данных, используя второй как операнд для умножителя.

Входной порт Y может получать данные из регистрового файла MY или из регистра MF. Регистровый файл содержит два регистра – MY0 и MY1. Эти регистры доступны на чтение и запись по шине данных памяти данных и на запись – по шине данных памяти программ. Выход регистрового файла MY – двухпортовый, что позволяет одновременно считывать содержимое одного из регистров через шину данных, используя второй как операнд для умножителя.

Данные с выхода устройства сложения/вычитания передаются либо в регистр MR, либо в регистр MF. MF – это регистр обратной связи, который позволяет использовать биты 16…31 результата, как операнд Y уже в следующем цикле. Регистры результата MR0, MR1, MR2 могут загружаться непосредственно через шину данных памяти данных. На чтение эти регистры доступны через шину данных памяти данных и шину результата R.

Любой из регистров MAC может быть считан и записан в течение одного и того же цикла. Чтение производится в начале цикла, запись – в конце. Это позволяет использовать регистр как источник операнда для умножителя и в этом же цикле загружать в этот регистр из памяти значение операнда для следующего цикла.

MAC имеет двойной банк своих регистров (на рисунке показано тенями). Одновременно могут быть доступны регистр только из одного банка (по умолчанию используется банк 0). Переключение банков выполняется командами ena sec_reg и dis sec_reg , либо установкой/сбросом нулевого бита регистра MSTAT. Такой механизм обеспечивает быстрое переключение контекстов.

MAC может выполнять перемножение знаковых и беззнаковых чисел в различных комбинациях (в ассемблерных командах MAC есть поле знака операндов, принимающее значение SS, UU, SU, US или RND).

Арифметико-логическое устройство

Устройство умножения с накоплением

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.