|

x4 |

x3 |

x2 |

x1 |

y |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

2 |

0 |

0 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

0 |

|

6 |

0 |

1 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

0 |

|

10 |

1 |

0 |

1 |

0 |

0 |

|

11 |

1 |

0 |

1 |

1 |

0 |

|

12 |

1 |

1 |

0 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

0 |

|

14 |

1 |

1 |

1 |

0 |

1 |

|

15 |

1 |

1 |

1 |

1 |

1 |

1.2 Мінімальні форми, реалізація в базисах І-НЕ, АБО-НЕ, І-АБО-НЕ

Побудуємо карти Карно для заданої функції:

Рисунок 1.1 – Карта Карно для одиниць

Рисунок 1.2 – Карта Карно для нулів

З рисунків 1.1, 1.2 зчитаємо мінімальні форми, об’єднуючи сусідні клітинки:

МДНФ:

МКНФ:

Приведемо зображення даних форм в базисах і зазначимо складність:

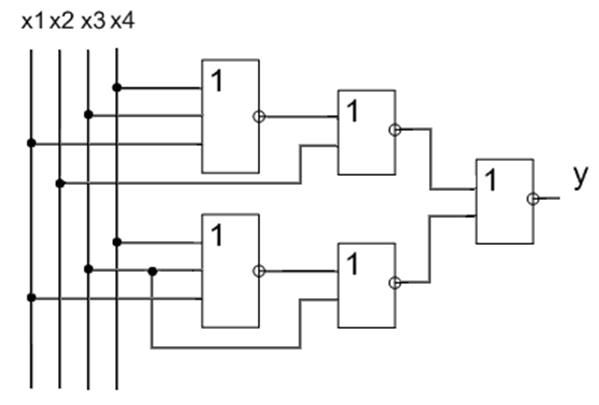

І-НЕ:

![]() , складність q = 6/10

, складність q = 6/10

АБО-НЕ:

![]() , складність q = 7/12

, складність q = 7/12

І-АБО-НЕ:

![]() , складність q = 6/11

, складність q = 6/11

Рисунок 1.3 – Реалізація в базисі І-НЕ

Рисунок 1.4 – Реалізація в базисі

АБО-НЕ

Рисунок 1.5 – Реалізація в базисі І-АБО-НЕ

1.3 Редукція в базисі АБО-НЕ

Для виконання редукції додамо додаткові клітинки, позначені зірочками:

Рисунок 1.6 – Карта Карно для редукції

Зчитуємо з рис. 1.6:

Складність до редукції рівна складності після редукції.

Для технічного проектування оберемо схему рис. 1.3, оскільки в такому випадку два корпуси мікросхем використовуються максимально (залишається невикористаним лише один вентиль, у порівнянні з схемою рис. 1.5, де не використовуються чотири з шести інверторів та частина схеми АБО-НЕ (К155ЛР3)).

1.4 Елементи технічного проектування пристрою

Для проектування візьмемо мікросхеми серії К155: К155ЛА3 та К155ЛА4, деякі параметри яких приведені нижче в таблиці 1.2.

Таблиця 1.2 – Параметри мікросхем

|

Тип |

Uж, В |

Iсп, мА |

І10, мА |

І11, мА |

І21, мА |

U20, В |

U21, В |

tзт, нс |

|

DD1-К155ЛА3 |

5 |

22 |

1,6 |

0,04 |

0,05 |

0,4 |

2,4 |

22 |

|

DD2-К155ЛА4 |

5 |

16,5 |

1,6 |

0,04 |

0,05 |

0,4 |

2,4 |

22 |

Схема спроектованого пристрою наведена на рис. 1.7

Рисунок 1.7 – Схема спроектованого пристрою

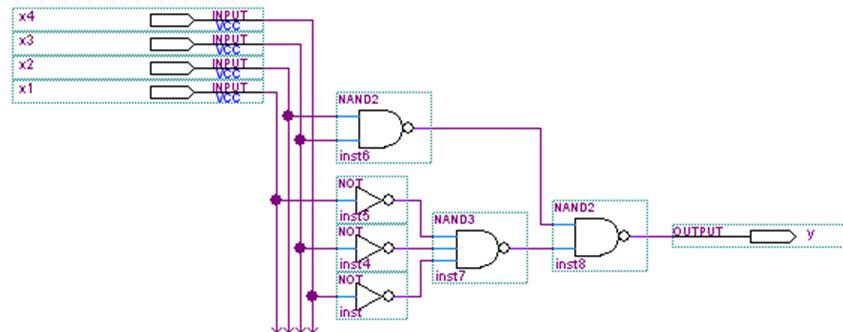

1.5 Автоматичне проектування пристрою в графічному редакторі Quartus II

Зберемо в графічному редакторі реалізації в базисах І-НЕ, АБО-НЕ, І-АБО-НЕ:

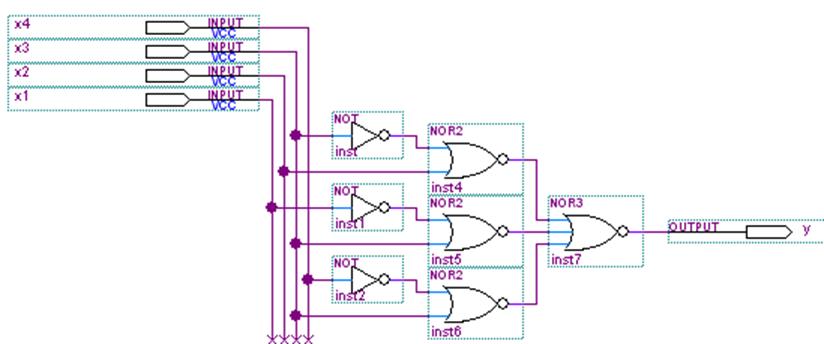

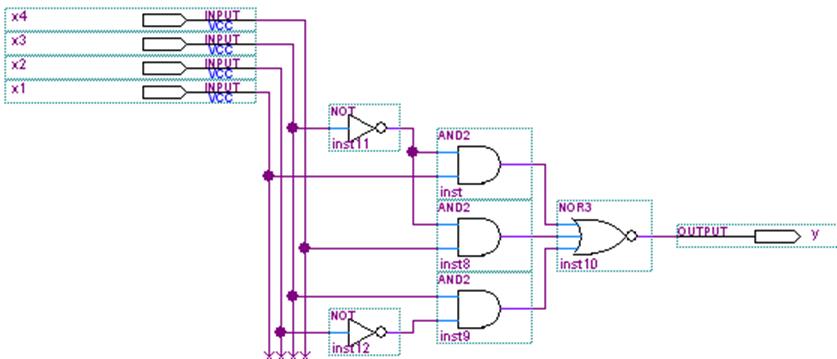

Рисунок 1.8 – Реалізація в базисі І-НЕ

Рисунок 1.9 – Реалізація в базисі АБО-НЕ

Рисунок 1.10 – Реалізація в базисі І-АБО-НЕ

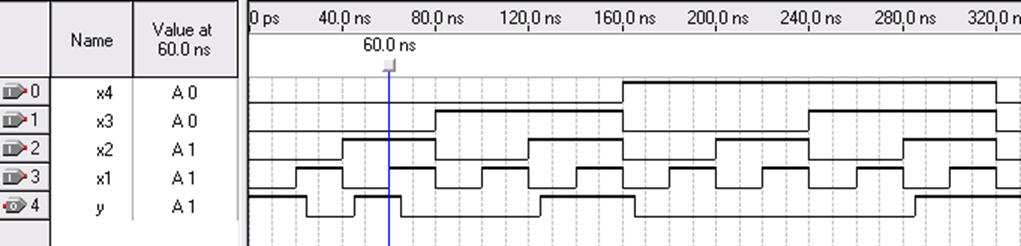

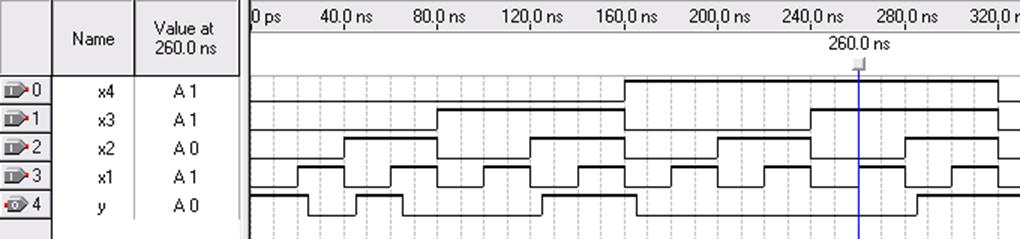

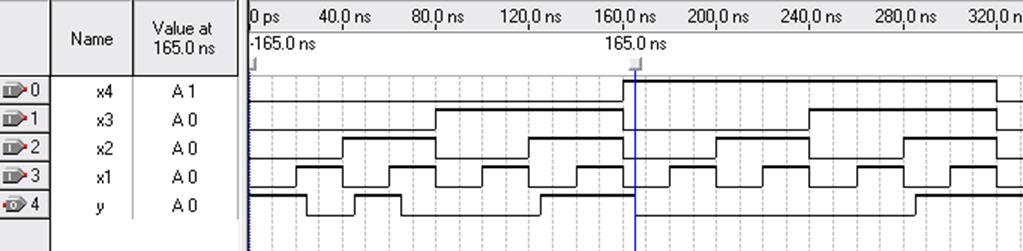

Приведемо файли часових діаграм всіх трьох реалізацій відповідно:

Рисунок 1.11 – Часові діаграми різних реалізацій

З отриманих діаграм видно, що вони повністю співпадають, що свідчить про правильність розрахунків і моделювання.

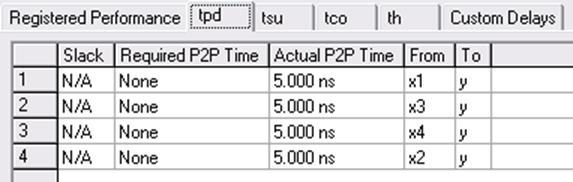

Здійснимо тепер аналіз швидкодії приладу за допомогою інструменту Classic Timing Analyzer Tool:

Рисунок 1.12 – Результати аналізу швидкодії

Як видно з рис. 1.12, затримка вихідного сигналу від вхідних становить 5 нс.

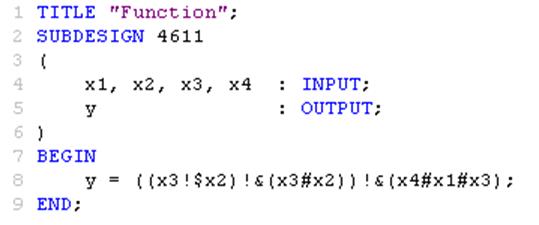

1.6 Автоматичне проектування пристрою в текстовому редакторі Quartus II

Створимо текстовий файл, в який введемо вираз заданої функції безпосередньо з технічного завдання:

Рисунок 1.13 – Опис заданої функції мовою AHDL

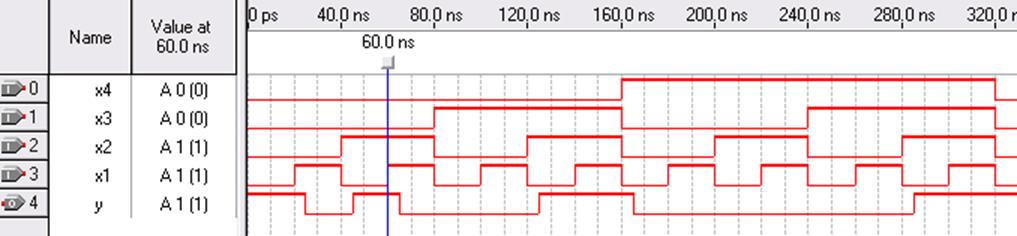

Скомпілюємо проект і порівняємо його часові діаграми з часовими діаграмами реалізацій спрощених функцій методом автоматичного порівняння:

Рисунок 1.14 – Автоматичне порівняння часових діаграм

Часові діаграми зображені червоним кольором, що свідчить про те, що в результаті автоматичного порівняння вони повністю співпадають.

2 ПРОЕКТУВАННЯ ПРИСТРОЮ НА ЦКП

2.1 Синтез дешифратора семисегментного коду

Спроектуємо дешифратор семисегментного коду для індикації знаків 0, 1, 2, 3, 4, 5, 6, 7, 8 на основі двійкового дешифратора.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.