U0=Eж.макс-I0RR £ U0макс. (4.12)

При вимкнених усіх М елементів з вільним колектором з об’єднаними виходами струм через резистор R замикається до їх виходів та входів БЕ-навантажень:

(4.13)

(4.13)

і вихідна напруга має бути не нижчою мінімально припустимого рівня лог. 1:

U1=Eж.мiн-I1RR ³U1мiн. (4.14)

Згідно з (4.12, 4.13) опір R розраховуємо за виразом

(Eж.макс-U0макс)/I0R £R £(Eж.мiн-U1мiн)/I1R. (4.15)

Приклад. Розрахуємо опір R для схеми на рис. 4.10,д при М=2, параметрах БЕ з вільним колектором: I0вих=16 мА, I1вих=0,25 мА, навантаженням, як у прикладах п.1 та нестабільністю напруги джерела живлення ±5%.

За (4.11), (4.13) маємо I0R=12,8 мА, I1R=0,78 мА; згідно з (4.15) 0,38 кОм ££R £3,01 кОм. З міркувань швидкодії вибираємо опір ближчим до меншоі межі: R=470 Ом.

Таким чином, базовою є схема елемента ТТЛ зі складним інвертором, яка виконує функцію І-НЕ. Середній час затримки поширення під час перемикання універсального елемента ТТЛ становить порядку 10 нс; в обох станах забезпечується низький вихідний опір, завдяки чому елемент здатний працювати на досить значну ємність навантаження. Внаслідок виникнення сплеску струму в шині живлення протягом перемикання утворюються завади, тому для їх пригнічення вдаються до конструктивних заходів (раціонально розташовують з’єднувальні шини, застосовують фільтрувальні конденсатори в колі живлення тощо).

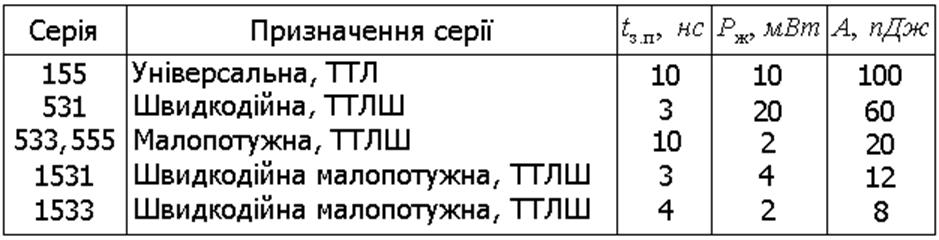

У цифровій та мікропроцесорній техніці широко вживаються різні модифікації елемента, зокрема, з трьома станами виходу, що дозволяє об’єднувати кілька елементів – передавачів інформації до спільної лінії в режимі часового мультиплексування. З метою підвищення швидкодії без збільшення споживаної потужності впроваджено серії ТТЛШ, в яких енергія перемикання менша, ніж в елементів ТТЛ (середні значення параметрів деяких серій подано в табл. 4.1). Елементи ДТЛ, що застосовуються в сучасних малопотужних, а також завадостійких серіях, звичайно відносять до класу ТТЛ, бо за параметрами і технологією вони сумісні з елементами ТТЛ.

Таблиця 4.1

§4.2. БАЗОВІ ЕЛЕМЕНТИ ЕСЛ

4.2.1. Перемикач струму

Головна перевага ІС емітерно-сполученої логіки (ЕСЛ) полягає в їх великій швидкодії. Завдяки функційній та схемотехнічній гнучкості, відпрацьованості технології ІС ЕСЛ набули поширення як елементна база швидкодійних пристроїв; засвоєно випуск біля 50 типономіналів ІС.

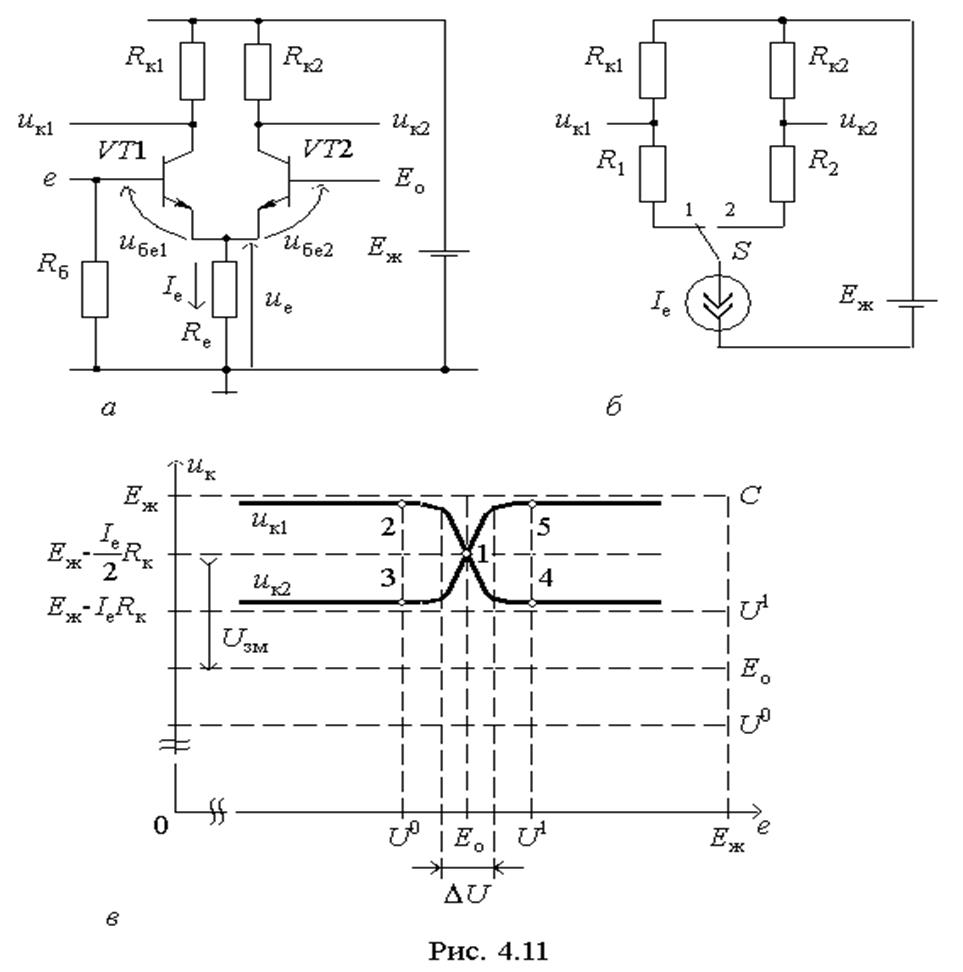

Основою БЕ ЕСЛ є підсилювальний

диференційний каскад (ДК) за схемою з несиметричним входом е та

несиметричними виходами uк1, uк2 (рис. 4.11,а). До складу ДК входять

керувальне плече на транзисторі VT1 і опорне – на VT2, до входу

якого прикладено постійну напругу Eо від джерела опорної напруги

(ДОН), що живиться від джерела живлення Eж. Завдяки ДОН і негативному зворотному зв’язку за струмом, який здійснюється через опір Rе, забезпечується стабілізація параметрів ДК під час зміни температури середовища або напруги живлення, старіння елементів.

Як видно зі схеми, в ДУ завжди виконується співвідношення

ue=e-uбе1=Eо-uбе2. (4.16)

З огляду на те, що на емітерному переході відчиненого транзистора напруга Uпр майже незмінна, емітерний струм можна обчислити як Iе=ue/Rе=(Eо-Uпр)/Rе, тобто він визначається приблизно сталими величинами.

Тому емітерне коло на еквівалентній схемі (рис. 4.11,б) репрезентують генератором стабільного струму (ГСС) Iе. Практично ГСС реалізується у вигляді опору Rе (наприклад, у серії 500) або транзисторного каскаду, що живиться від ДОН (у серії 1500).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.