Міністерство освіти і науки, молоді та спорту України

Харківський національний університет радіоелектроніки

Звіт

До лабораторної роботи №6

З дисципліни: «Теорія Електрозв’язку»

|

Виконали Ст. гр. ТК-11-1 Корякін Д.С. Полушина К.С. Баляба Л.О. |

Перевірив Астраханцев А. А. |

Харків 2013

Свёрточные коды

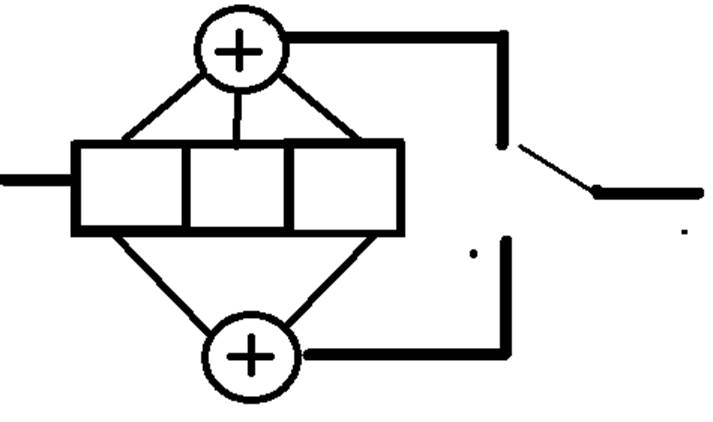

1.Построение кодера

1.1 Кодер состоит из регистра и сумматоров. Количество ячеек в регистре равно старшей степени порождающего полинома плюс один, количество сумматоров равно количеству порождающих полиномов.

1.2 Если присутствует стрелочка от i-той ячейки к сумматору, то этот член полинома не равен нулю.

1.3 Основные характеристики кода: Относительная скорость кода R=k/n,

Где k-количество символов поступающих на входы кодера, n-количество символов одновременно формирующихся на выходах кодера (количество выходов равно количеству сумматоров, количество регистров равно количеству входов).

2.1 Выходные последовательности формируются до тех пор пока последний поступающий символ не покинет кодер. Если символы заканчиваются последовательность дополняется нулями. Выходные последовательности формируются поочерёдным подключением к каналу связи каждого из выходов.

Рисунок 1 – Схема кодера.

3Ход работы

1. Запустить программу Svert.exe.

2. Собрать заданный преподавателем вариант схемы кодера.

1. Активировав сумматор – подключить к нему необходимые ячейки.

2. Уменьшить до заданной величины количество бит регистра (блок управления установкой)

3. Исследование импульсного отклика кодера

1. В блоке управления установкой включить генератор единиц (Ген ‘1’)

2. Нажимая «Пошагово», записать в табл.1 состояния кодера, выходы сумматоров и выходную последовательность на каждом такте и итоговую.

Таблица 1

|

№ такта |

Входной поток |

Состояние кодера |

Сумматор 1 |

Сумматор 2 |

Выход |

|

1 |

1 |

100 |

1 |

1 |

11 |

|

2 |

0 |

010 |

1 |

0 |

10 |

|

3 |

0 |

001 |

1 |

1 |

11 |

4. Исследование алгоритма кодирования

4.1 Включить генератор случайной битовой последовательности (блок управления установкой) и для 10 бит входной последовательности – сформировать выходную последовательность, результаты записывать в таблицу 2.

Таблица 2

|

№ такта |

Входной поток |

Состояние кодера |

Сумматор 1 |

Сумматор 2 |

Выход |

|

1 |

1 |

100 |

1 |

1 |

11 |

|

2 |

1 |

110 |

0 |

1 |

01 |

|

3 |

1 |

111 |

1 |

0 |

10 |

|

4 |

0 |

011 |

0 |

1 |

01 |

|

5 |

0 |

001 |

1 |

1 |

11 |

|

6 |

1 |

100 |

1 |

1 |

11 |

|

7 |

0 |

010 |

1 |

0 |

10 |

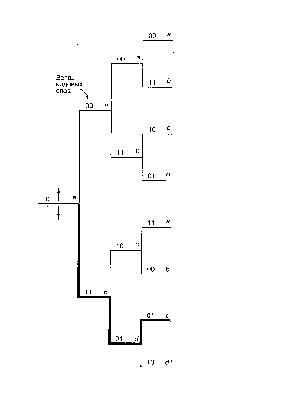

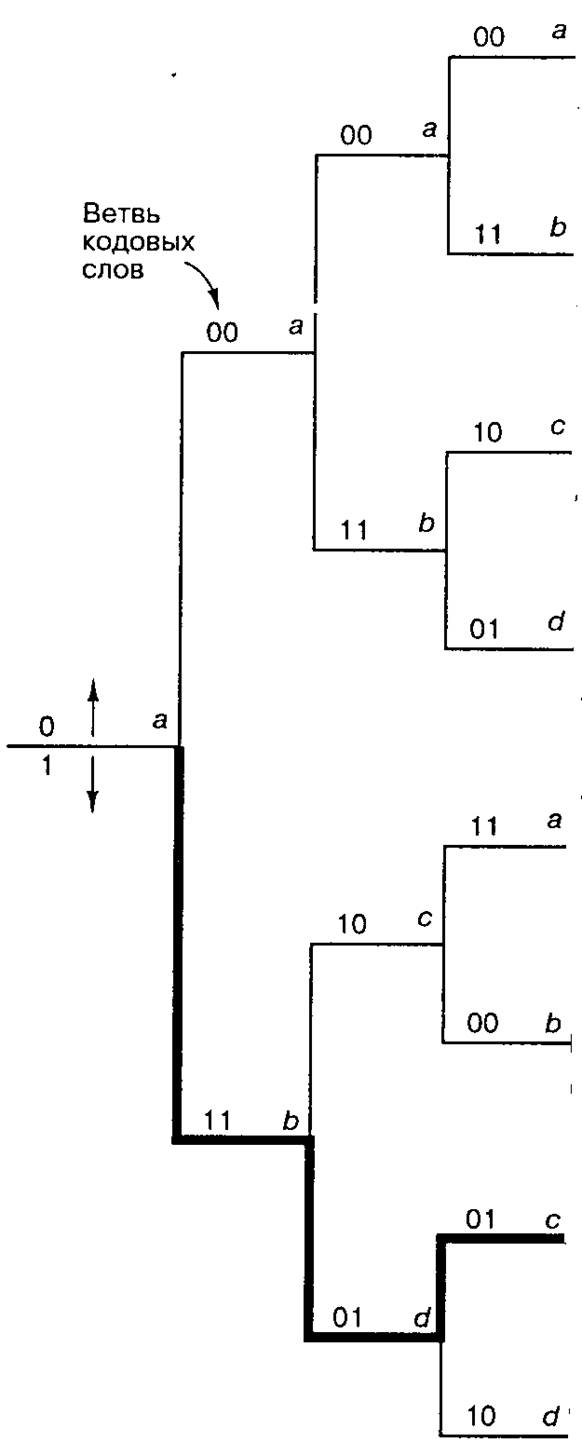

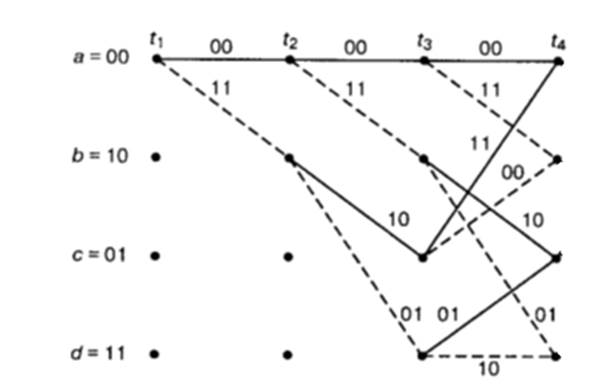

5. Исследование методов описания сверточных кодов

1. Для заданной схемы кодера построить древовидную диаграмму, используя описание в файле Svert_Kod.pdf.

2. Для заданной схемы кодера построить решетчатую диаграмму, используя описание в файле Svert_Kod.pdf. Определить величину свободного расстояния (просвета ).

3. Привести описание исследуемой схемы при помощи полиномов.

6. Порождающий полином:

7. g1(x)=1+x+x2

8. g2(x)=1+x2

9. Исследование возможностей кода по исправлению ошибок

1. Задать схему кодера (рис.1). Включить генератор случайной битовой последовательности. Не забудьте ограничить число ячеек в кодере!

2. Задать в блоке управления линией связи кратность ошибок 1 из 3. Отследить возможности кодера по исправлению ошибок.

3. Изменяя кратность ошибки, начиная с 1 из 3 и до 1 из 7, отследить возможности кодера по исправлению ошибок.

Кодер декодирует и исправляет ошибки кратность которых меньше 1/2

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.