НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

Выполнил |

|

Студент |

|

|

Группа |

|

|

Дата |

Принял |

|

Преподаватель |

|

Дата |

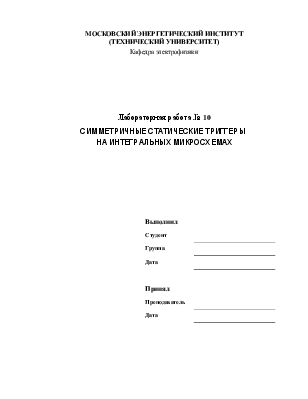

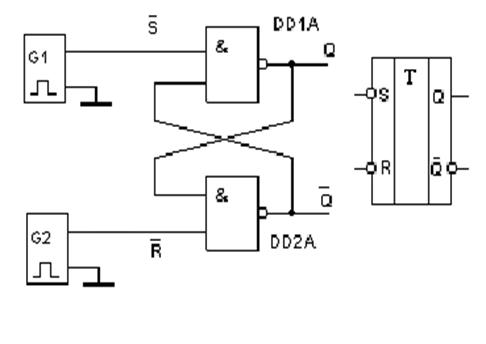

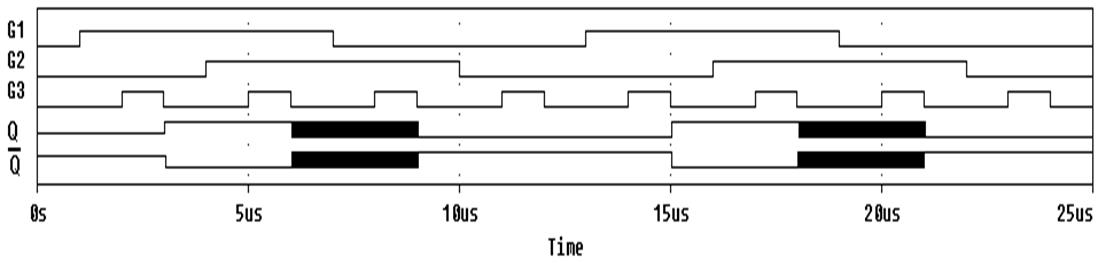

Схема лабораторной установки

Рис. 1. Лицевая панель лабораторной работы № 10

Подготовка к работе:

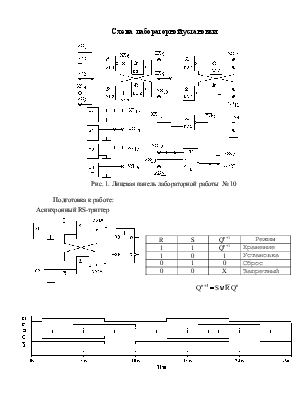

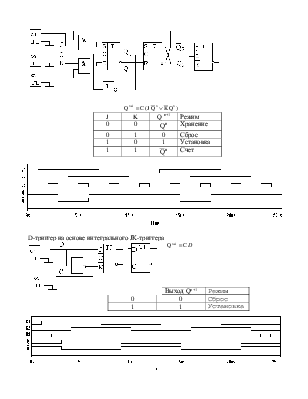

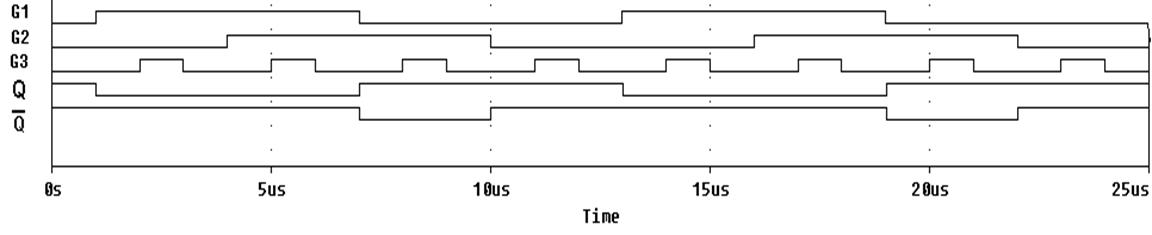

Асинхронный RS-триггер

|

R |

S |

Qn+1 |

Режим |

|

1 |

1 |

Qn+1 |

Хранение |

|

1 |

0 |

1 |

Установка |

|

0 |

1 |

0 |

Сброс |

|

0 |

0 |

X |

Запретный |

![]()

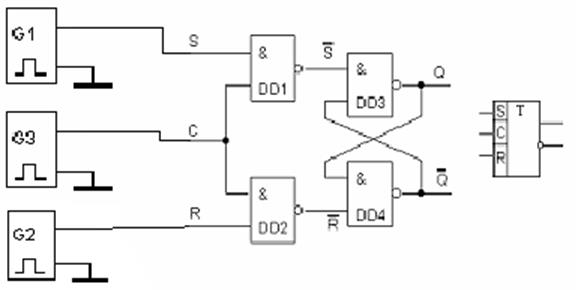

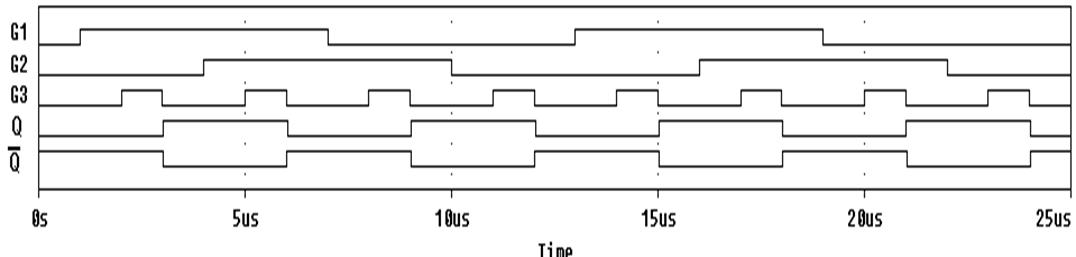

Тактируемый RS-триггер

![]()

|

R |

S |

Qn+1 |

Режим |

|

0 |

0 |

Qn+1 |

Хранение |

|

0 |

1 |

1 |

Установка |

|

1 |

0 |

0 |

Сброс |

|

1 |

1 |

X |

Запретный |

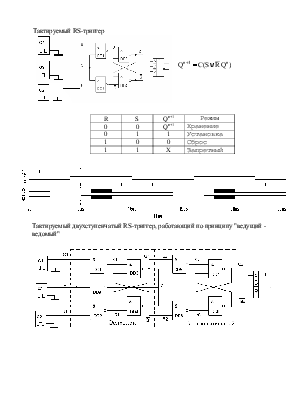

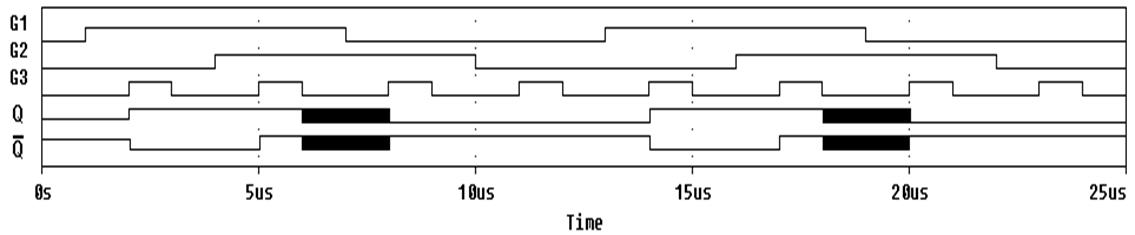

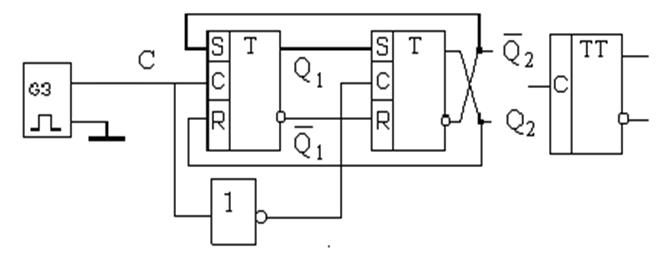

Тактируемый двухступенчатый RS-триггер, работающий по принципу "ведущий - ведомый"

|

R |

S |

Qn+1 |

Режим |

|

0 |

0 |

Qn+1 |

Хранение |

|

0 |

1 |

1 |

Установка |

|

1 |

0 |

0 |

Сброс |

|

1 |

1 |

X |

Запретный |

T-триггер на базе двухступенчатого RS-триггера

|

Вход Т |

Выход Qn+1 |

Режим |

|

0 |

Qn+1 |

Хранение |

|

1 |

Qn+1 |

Счет |

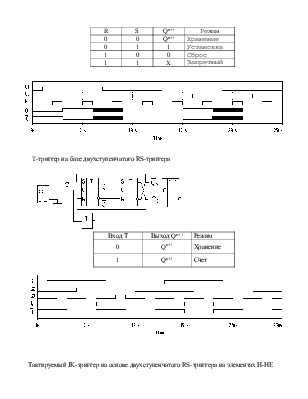

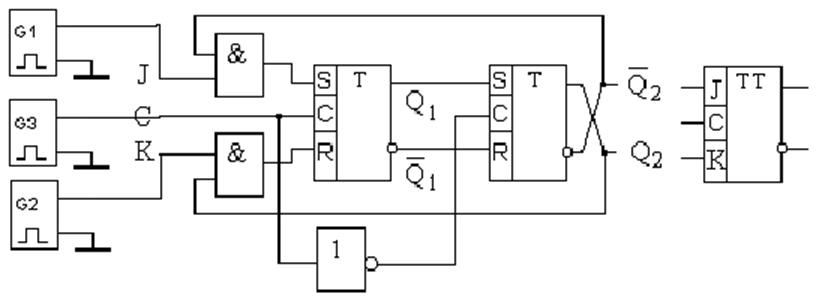

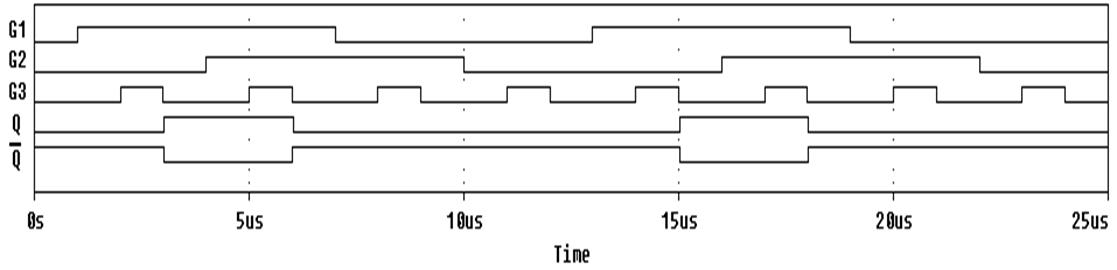

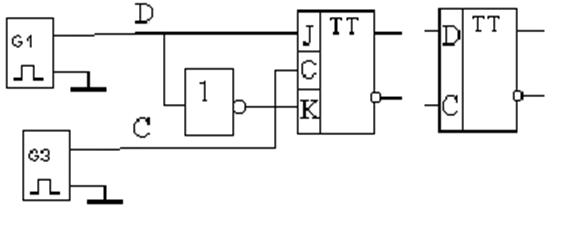

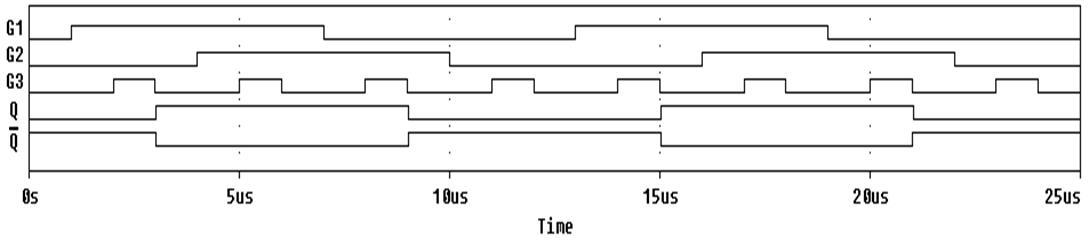

Тактируемый JK-триггер на основе двухступенчатого RS-триггера на элементах И-НЕ

![]()

|

J |

K |

Q n+1 |

Режим |

|

0 |

0 |

|

Хранение |

|

0 |

1 |

0 |

Сброс |

|

1 |

0 |

1 |

Установка |

|

1 |

1 |

|

Счет |

D-триггер на основе интегрального JK-триггера

|

Вход D |

Выход Qn+1 |

Режим |

|

0 |

0 |

Сброс |

|

1 |

1 |

Установка |

![]()

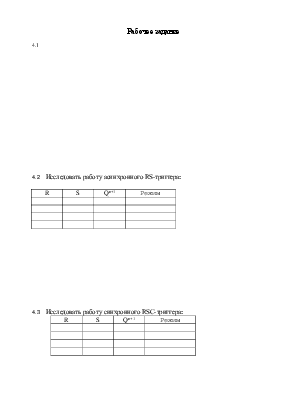

Рабочее задание

4.1

4.2 Исследовать работу асинхронного RS-триггера:

|

R |

S |

Qn+1 |

Режим |

4.3 Исследовать работу синхронного RSC-триггера:

|

R |

S |

Qn+1 |

Режим |

4.4 Исследовать работу тактируемого двухступенчатого RS-триггера:

|

R |

S |

Qn+1 |

Режим |

4.5 Исследовать работу JK-триггера:

|

J |

K |

Q n+1 |

Режим |

4.6 Исследовать работу D-триггера:

|

Вход D |

Выход Qn+1 |

Режим |

4.7 Исследовать работу Т-триггера:

|

Вход Т |

Выход Qn+1 |

Режим |

4.8 Измерить время задержки распространения сигнала по счетному входу интегрального JK-триггера и JK-триггера на элементах И-НЕ:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.