а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS-триггера Таблица 3

|

№ |

R’ |

S’ |

Q n+1 |

Q’ n+1 |

|

1 |

1 |

1 |

Q n |

Q’ n |

|

2 |

1 |

0 |

1 |

0 |

|

3 |

0 |

1 |

0 |

1 |

|

4 |

0 |

0 |

– |

– |

Анализ работы триггера (рисунки 4, а; 5, а) выполняется по следующему алгоритму:

- задать исходные значения выходов, например, Q n =0, Q’ n =1;

- выбирать значения входных сигналов R, S в соответствии с таблицей истинности;

- выполнить логические операции c заданными Q n и выбранными значениями R, S;

- новые (полученные) значения выходов Q n+1подать на входы и еще раз выполнить логические операции из-за возможности появления неустойчивых состояний.

На основе RS-триггера получен ряд триггеров с различными функциональными возможностями. Например, синхронный RS-триггер (рис. 6), его таблица истинности табл. 4.

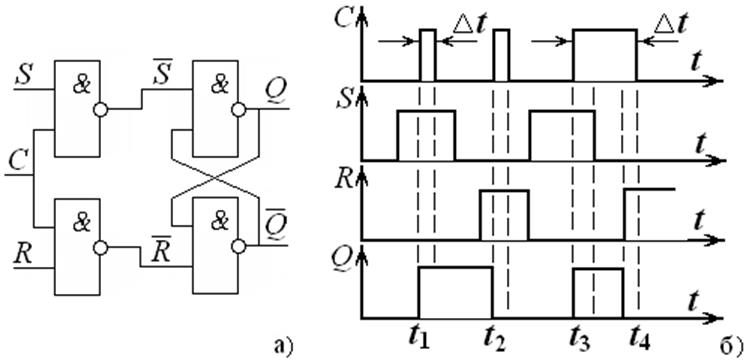

Рис. 6 Синхронный RS-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности синхронного RS-триггера Таблица 4

|

№ |

C |

R |

S |

Q n+1 |

Q’ n+1 |

|

1 |

1 |

0 |

0 |

Q n |

Q’ n |

|

2 |

1 |

0 |

1 |

1 |

0 |

|

3 |

1 |

1 |

0 |

0 |

1 |

|

4 |

1 |

1 |

1 |

– |

– |

|

5 |

0 |

X |

X |

Q n |

Q’ n |

X – любое значение переменной, которая не оказывает влияния на результат.

Считывание сигналов с информационных входов R, S происходит при наличии тактового сигнала C на интервале времени Dt, когда триггер работает как статическое устройство. Если в течение этого интервала по какой-либо причине происходит изменение входных сигналов R, S, то оно оказывает влияние на состояние выходов (интервал времени t3 – t4).

Чтобы сократить время считывания (приблизительно до пяти наносекунд) и таким образом повысить помехозащищенность триггера, тактовый вход C делают динамическим.

3 D-триггер

Схема D-триггера (рис. 7) имеет один информационный вход D и тактовый вход C, его таблица истинности табл. 5.

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

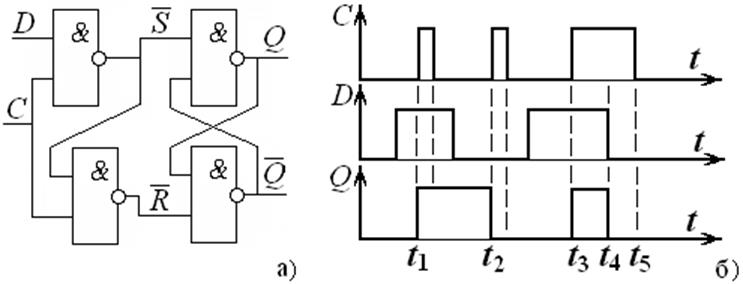

Рис. 7 D-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности D-триггера Таблица 5

|

№ |

C |

D |

Q n+1 |

|

1 |

1 |

0 |

0 |

|

2 |

1 |

1 |

1 |

|

3 |

0 |

X |

Q n |

На рисунке 7 представлен синхронный потенциальный D-триггер. Если при наличии тактового сигнала C (интервал t3 – t5), происходит изменение входного сигнала D (в момент времени t4), то это оказывает влияние на состояние выходов.

Чтобы повысить помехозащищенность триггера, тактовый вход C делают динамическим.

Если в схему D-триггера добавить разрешающий вход V, то такое устройство называется DV-триггером (рис. 8), таблица истинности табл. 6.

|

Таблица истинности DV-триггера Таблица 6 |

|

||||

|

№ |

V |

C |

D |

Q n+1 |

|

|

1 |

1 |

1 |

0 |

0 |

|

|

2 |

1 |

1 |

1 |

1 |

|

|

3 |

0 |

0 |

X |

Q n |

|

|

4 |

0 |

1 |

X |

Q n |

|

|

5 |

1 |

0 |

X |

Q n |

|

Рис. 8 DV-триггер

Данные триггеры применяются:

- для задержки прохождения сигнала до появления тактового импульса;

- в регистрах и счетчиках;

- в запоминающих устройствах, требующих большого числа простых ячеек памяти.

4 T-триггер

Схема T-триггера (рис. 9) имеет один информационный динамический вход T, его таблица истинности табл. 7. Если в схему T-триггера добавить разрешающий вход V, то такое устройство называется TV-триггером (по аналогии с DV-триггером).

Таблица истинности T-триггера Таблица 7

|

№ |

T |

Q n |

Q n+1 |

|

1 |

1 |

0 |

1 |

|

2 |

1 |

1 |

0 |

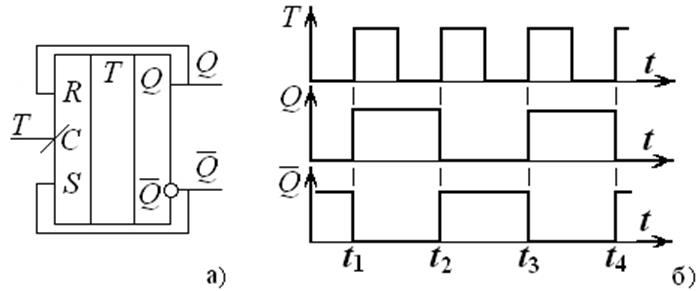

Рис. 9 T-триггер

на основе RS-триггера:

а – принципиальная схема; б – временные диаграммы работы

Согласно временной диаграмме, в исходном состоянии Q =0, Q’ =1, на входе R =0, S=1. По переднему фронту тактового импульса T=1 сигналы с выходов запишутся в триггер и установятся новые значения Q =1, Q’ =0 (в момент времени t1). Очередной тактовый импульс запишет их в триггер и в момент времени t2 установятся значения Q =0, Q’ =1.

Данный триггер применяется:

- для изменения знака двоичного числа в арифметико-логическом устройстве;

- в счетчиках, делителях частоты;

- в регистрах.

5 Приоритетные триггеры

Триггеры, у которых одни входы имеют преимущество над другими в установлении сигналов на выходе, называются приоритетными.

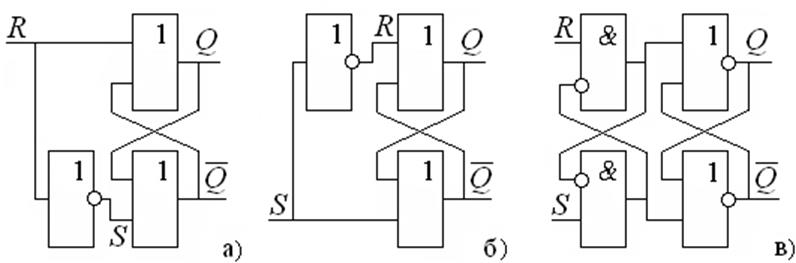

К таким устройствам относятся разновидности RS–триггера, а именно: R, S, E-триггеры (рис. 10, таблица истинности табл. 8). Последняя строка этой таблицы определяет приоритет соответствующего входа.

Таблица истинности RS -триггеров Таблица 8

|

R -триггер |

S -триггер |

E -триггер |

||||||||

|

R |

S |

Qn+1 |

R |

S |

Qn+1 |

R |

S |

Qn+1 |

||

|

0 |

0 |

Q n |

0 |

0 |

Q n |

0 |

0 |

Q n |

||

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

||

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

||

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Q n |

||

Схема E-триггера устанавливает преимущество входного сигнала R или S, который появился на входе первым с помощью логической операции Импликация. Пришедший первым сигнал (логическая единица) инвертируется и устанавливает запрет на поступление сигнала на второй вход.

Рис. 10 Приоритетные триггеры на основе RS-триггера:

а – R-триггер; б – S-триггер; в – E-триггер

Пример E-триггер исключает зажигание сигналов светофора одинакового цвета для различных направлений движения транспорта.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.