13. согласующие элементы

В состав системы управления входят функциональные элементы разнородные по типу сигнала, роду тока, по сопротивлению, мощности и т.п. (датчики тока, напряжения, регуляторы, ЗИ), поэтому при соединении элементов необходимо согласование их характеристик. Эту функцию и выполняют согласующие элементы. К ним относятся: фазовые детекторы, согласующие род тока, гальванические разделители, ЦАП и АЦП, согласующие тип сигнала, эмиттерные повторители, согласующие входные и выходные сопротивления, делители мощности.

Фазовый детектор (ФД) (фазочувствительный усилитель или фазочувствительный выпрямитель, фазовый дискриминатор, демодулятор.)

Назначение ФД – преобразование входного напряжения переменного тока Uвх m в выходное напряжение постоянного тока Uвых, полярность и амплитуда которого, зависят от фазы входного напряжения φ, т.е. ФД имеет две входные координаты Uвх m и φ и одну выходную Uвых (рис. 13.1).

Рис. 13.1. Координаты фазового детектора

Различают два режима работы ФД:

– амплитудный режим, когда фаза φ входного напряжения остается постоянной (0 или π), а Uвх m = var и Uвых = f(Uвх m);

– фазовый режим, когда Uвх m = const, φ = var и Uвых = f(φ).

В амплитудном режиме ФД применяется как преобразователь сигнала рассогласования переменного тока в управляющий сигнал в следящих приводах постоянного тока; как преобразователь выходного сигнала тахогенератора переменного тока; как выходной каскад (демодулятор) в усилителях с промежуточным усилением на переменном токе. В фазовом режиме ФД применяют в системах управления, в которых контролируемой и управляемой величиной является плавно изменяющаяся фаза. В этом режиме ФД получает питание от фазовращающих устройств.

ФД, как правило, напряжение не усиливает, т.е. коэффициент усиления kфд ≈ 1.

|

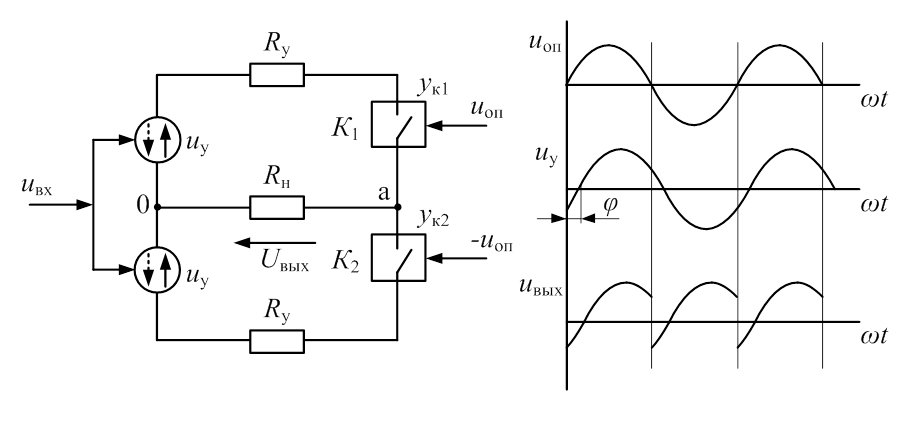

Рис. 13.2. Расчетная схема замещения двухполупериодного ФД |

Рис. 13.3. Диаграмма работы ФД |

Схема замещения двухполупериодного ФД соответствует нулевой схеме выпрямления (рис. 13.2), в которой вместо вентилей стоят ключи К1, К2.

uу – ЭДС источников управления, Rу – внутреннее сопротивление источника ЭДС управления. Состоянием ключей управляет опорная ЭДС uоп. в соответствии со следующим алгоритмом:

– при uоп > 0 включен K1, а К2 отключен, т.е. ук1 = 1, и ук2 = 0;

– при uоп <0, включен K2, К1 отключен и ук1 = 0, ук2 = 1.

алгоритм работы uвых = uу ук1 – uу ук2.

Подстановка ук1 = (1+sign uоп)/2 и ук2 = (1-sign uоп)/2 дает

uвых = uу sin uоп.

При замкнутом К1 uвых = uу

При замкнутом К2 uвых = –uу

Функция sign (сигнум) определяется следующим образом:

sign uоп = 0, при uоп = 0;

sign uоп = 1, при uоп > 0;

sign uоп = – 1, при uоп < 0.

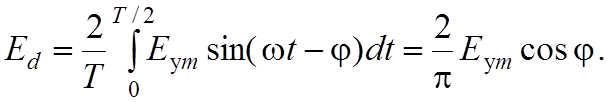

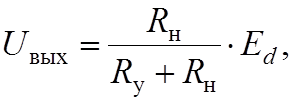

Если uоп = Eоп m sin ωt, uу = Eуm sin (ωt – φ), то среднее значение выпрямленной выходной ЭДС

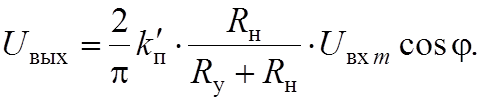

т.к. Eуm = k’п·Uвхm, а среднее значение выходного напряжения

то

то

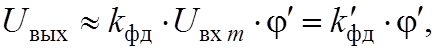

При φ = 0 = const (или φ = π = const) и Uвх m = var имеет место амплитудный режим, для которого характеристика управления линейна

Uвых = kфд·Uвх m,

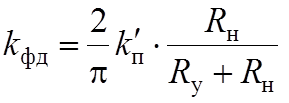

где

- коэффициент усиления ФД в

амплитудном режиме;

- коэффициент усиления ФД в

амплитудном режиме;

![]() - передаточный

коэффициент от входного напряжения к ЭДС управления.

- передаточный

коэффициент от входного напряжения к ЭДС управления.

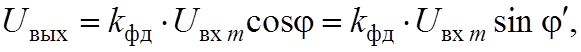

При Uвх m = const и φ = var имеет место фазовый режим, для которого

где

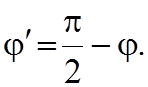

при малых φ’

где

– передаточный коэффициент ФД в

фазовом режиме

– передаточный коэффициент ФД в

фазовом режиме

Пример схемы ФД – двухполупериодная транзисторная схема (демодулятор в лабораторной работе №6).

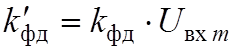

Рассмотрим схему интегрального ФД (рис. 13.4).

Рис. 13.4. схема интегрального ФД

Входным и опорным сигналами являются прямоугольные высокочастотные колебания. Опорное напряжение Uоп управляет транзисторным ключем VT. Когда Uоп > 0, транзистор заперт и на выходе DA напряжение не инвертируется т.е. Uвых = k·Uвх. Когда Uоп < 0, VT открыт и выходное напряжение Uвых инвертируется, т.е. Uвых = – k·Uвх. при φ = 0 на выходе усилителя DA имеет место выпрямление и Uвых во всех полупериодах положительно. При противофазных колебаниях Uвх и Uоп (φ = π), напряжение Uвых < 0.

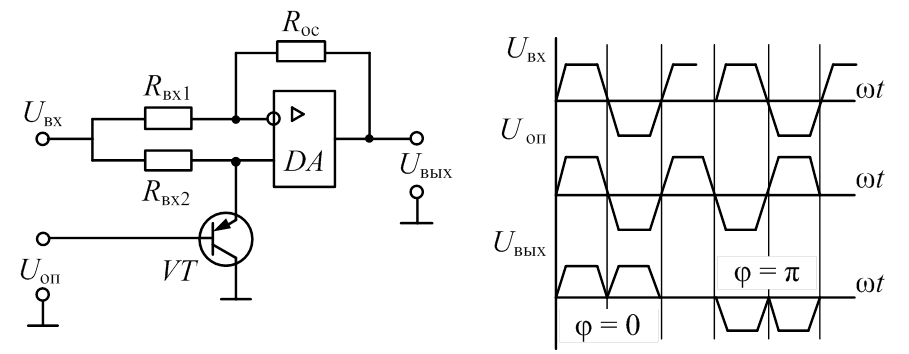

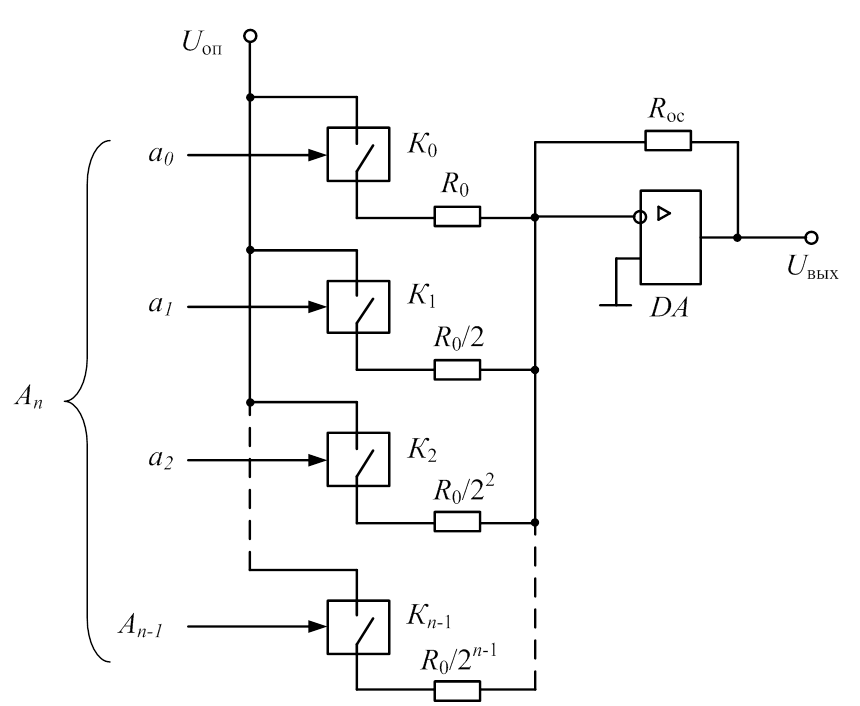

цифроаналоговые преобразователи (цап). ЦАП согласуют цифровую часть системы управления с аналоговой. Входная координата ЦАП – двоичное многоразрядное число Аn = an-1, … ai … a1 a0, а выходная координата – напряжения Uвых, формируемое на основе опорного напряжения (рис. 13.5).

Рис. 13.5. Основные координаты ЦАП

Схемы ЦАП строятся на основе резисторной матрицы, с помощью которой происходит суммирование токов или напряжений так, что выходное напряжение пропорционально входному числу. В составе ЦАП выделяют три части резисторная матрица, электронные ключи, управляемые входным числом и суммирующий усилитель (рис. 13.6).

Рис. 13.6.Схема нереверсивного ЦАП

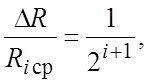

Каждому разряду входного числа An соответствует сопротивление

Ri = R0/2i, где R0 –

сопротивление младшего разряда.

Резистор Ri подключается к источнику опорного напряжения Uоп через электронный ключ Ki, который замкнут при ai = 1 и разомкнут при ai = 0. В зависимости от значения ai сопротивление входной цепи для i-го разряда равно

Тогда, для ai = 0 Ri=¥, т.е. цепь разорвана, а для ai = 1 цепь включена и имеет сопротивление R0/2i.

Выходное напряжение операционного усилителя DA, суммирующего входные токи, находится по выражению

Т.о., характеристика управления ЦАП Uвых = f(An) имеет ступенчатую форму с дискретностью по напряжению, соответствующего младшему разряду

Величина ΔU0 = kцап является одновременно и усредненным передаточным коэффициентом.

Недостаток данной схемы, – необходимы разные номиналы

входных разрядных сопротивлений, и кроме того, чем старше разряд, тем меньше

сопротивления и больше ток, и тем выше требования к классу точности резистора

по значению сопротивлению. Она равна  и при n

= 10 точность изготовления составит около 0,1 %, что практически не реализуемо.

Поэтому данная схема применяется для ЦАП с небольшой разрядностью.

и при n

= 10 точность изготовления составит около 0,1 %, что практически не реализуемо.

Поэтому данная схема применяется для ЦАП с небольшой разрядностью.

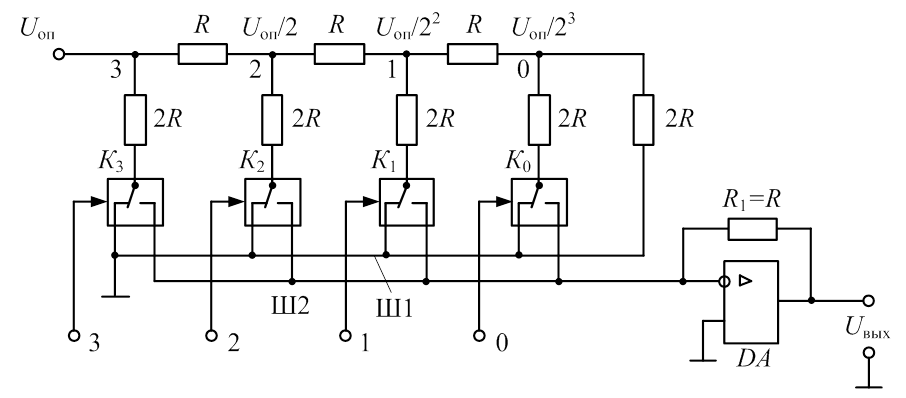

Для устранения этих недостатков была разработана схема, в которой используется резисторная матрица с двумя номинальными сопротивлениями R и 2R для любого числа разрядов (рис. 13.7). Все резисторы обтекаются неизменными токами независимо от положения электронных ключей K0 – K3.

Управляемые ключи, в зависимости от входного числа Аn = a3 a2 a1 a0 могут быть либо замкнуты на шину Ш1, если соответствующее ai = 0, либо на шину Ш2, если ai= 1.

Рис. 13.7. Схема ЦАП с резисторной матрицей R-2R

Рис. 13.7. Схема ЦАП с резисторной матрицей R-2R

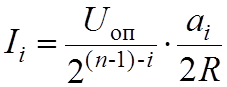

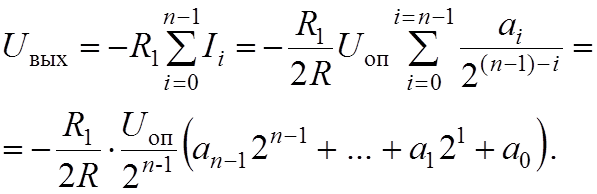

На резисторах R и 2R в точках 3, 2, 1, 0 происходит последовательное деление пополам напряжения и тока, при этом ток i-го разряда протекающий в шину Ш2 определяется формулой

Выходное напряжение Uвых

Дискретность и усредненный передаточный коэффициент

ЦАП в этой схеме  если R1 = R

то

если R1 = R

то

примерами серийно выпускаемых ЦАП являются микросхемы К572ПА1А – десятиразрядный ЦАП, К572ПА2А – двенадцатиразрядный ЦАП.

аналоговые цифровые преобразователи (ацп). АЦП преобразует входное непрерывное по форме напряжение в пропорциональное ему число (обычно в двоичном коде).

Каждому выходному числу Ai соответствует диапазон изменения входного напряжения.

,

,

где Uэi = ΔU0·i – эталонное значение входного напряжения соответствующее выходному числу Аi;

ΔU0 – дискретность по напряжению, соответствующего единице младшего разряда выходного числа;

i – десятичное число.

При n – разрядном АЦП общее число отличных от нуля эталонных уровней входного напряжения, отличающих друг от друга на ΔU0 равно максимальному выходному числу N = 2n – 1. Усредненный передаточный коэффициент АЦП определяется как обратная величина соответствующего коэффициента ЦАП

kацп = 1/ΔU0.

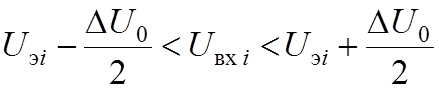

В работе АЦП можно выделить основные операции: сравнение входного и эталонных напряжений, определения номера уровня, формирование выходного числа в заданном коде. АЦП делятся на два основных типа: параллельного (рис. 13.8) и последовательного действия (рис. 13.9).

Рис. 13.8. Схема АЦП параллельного действия

С помощью резисторного делителя выделяются уровни эталонного напряжения в токах 1, 2, …, N. Сравнение Uвхi и Uэi выполняется на компараторах К1 – Кn, в качестве которых используются операционные усилителя с однополярными выходами.

При Uвхi – Uэi < ΔU0/2 на выходе компараторов – нулевой сигнал, а при Uвхi – Uэi ≥ ΔU0/2, на выходах единицы, которые запоминаются D – триггерами.

Число единиц на выходах триггеров преобразуется с помощью шифратора CDв код n – разрядного двоичного числа An, равного i (i – это номер уровня в десятичном исчислении). Достоинство данной схемы АЦП – высокое быстродействие, недостаток – большое число компараторов и триггеров (2n – 1) (для восьмиразрядного АЦП необходимо 255 компараторов и столько же триггеров).

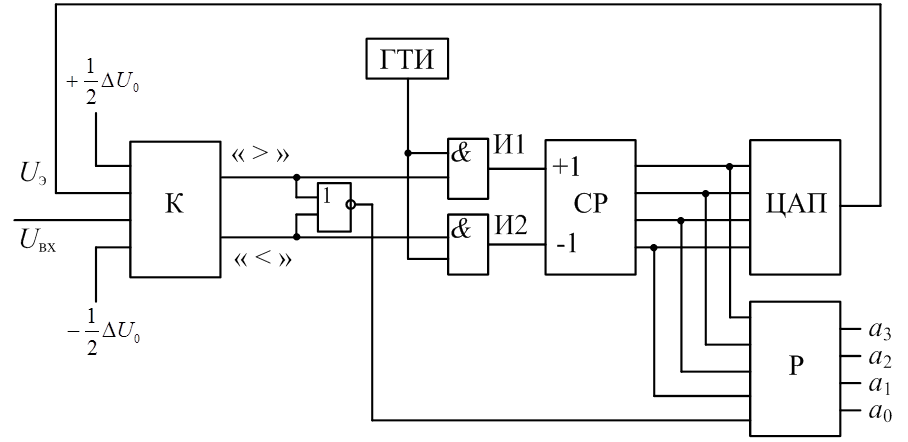

Существенно меньше элементов содержит АЦП последовательного действия (рис. 13.9).

Рис. 13.9. Схема АЦП последовательного действия (следящий АЦП)

Сравнения Uвх и Uэ выполняется на комбинированном аналоговом компараторе К с двумя выходами: “больше” (>) и “меньше” (<).

Если Uвх – Uэ > ΔU0/2,то единичный сигнал на выходе «>», при этом элемент И1 пропускает проводит тактовые импульсы на суммирующий вход (+1) реверсивного счетчика СР. Растёт выходное число СР, и соответственно увеличивается Uэ, формируемое ЦАП.

Если  , то единичный

сигнал появляется на выходе «<» при этом импульсы от генератора тактовых

импульсов через И2 проходят на вход вычитания (-1) СР и Uэ уменьшается. При

выполнения условия

, то единичный

сигнал появляется на выходе «<» при этом импульсы от генератора тактовых

импульсов через И2 проходят на вход вычитания (-1) СР и Uэ уменьшается. При

выполнения условия  на обоих выходах К

будут нулевые сигналы и элементы И1 и И2

оказываются закрыты для тактовых импульсов. Счётчик прекращает считать, и

число на его выходе появляется на выходе регистра Р. Разрешение на

запись числа в регистр дает единичный сигнал элемента ИЛИ–НЕ. Рассмотренная

схема относительно Uвх и Uэ представляет собой

замкнутую систему регулирования. Система отслеживает эталонным напряжением на

выходе ЦАП изменение входного напряжения с установившейся точностью

на обоих выходах К

будут нулевые сигналы и элементы И1 и И2

оказываются закрыты для тактовых импульсов. Счётчик прекращает считать, и

число на его выходе появляется на выходе регистра Р. Разрешение на

запись числа в регистр дает единичный сигнал элемента ИЛИ–НЕ. Рассмотренная

схема относительно Uвх и Uэ представляет собой

замкнутую систему регулирования. Система отслеживает эталонным напряжением на

выходе ЦАП изменение входного напряжения с установившейся точностью  , поэтому такие АЦП называют еще

следящими.

, поэтому такие АЦП называют еще

следящими.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.