Разряды До-Д3 регистра состояния устанавливаются одновременно с появлением сигнала КС соответствующего канала и сбрасываются сигналом СВР при чтении содержимого регистра состояния.

Считывание регистра состояний не влияет на Д4 (флаг обновления), его можно сбросить установкой нуля в разряд Д7 регистра режима.

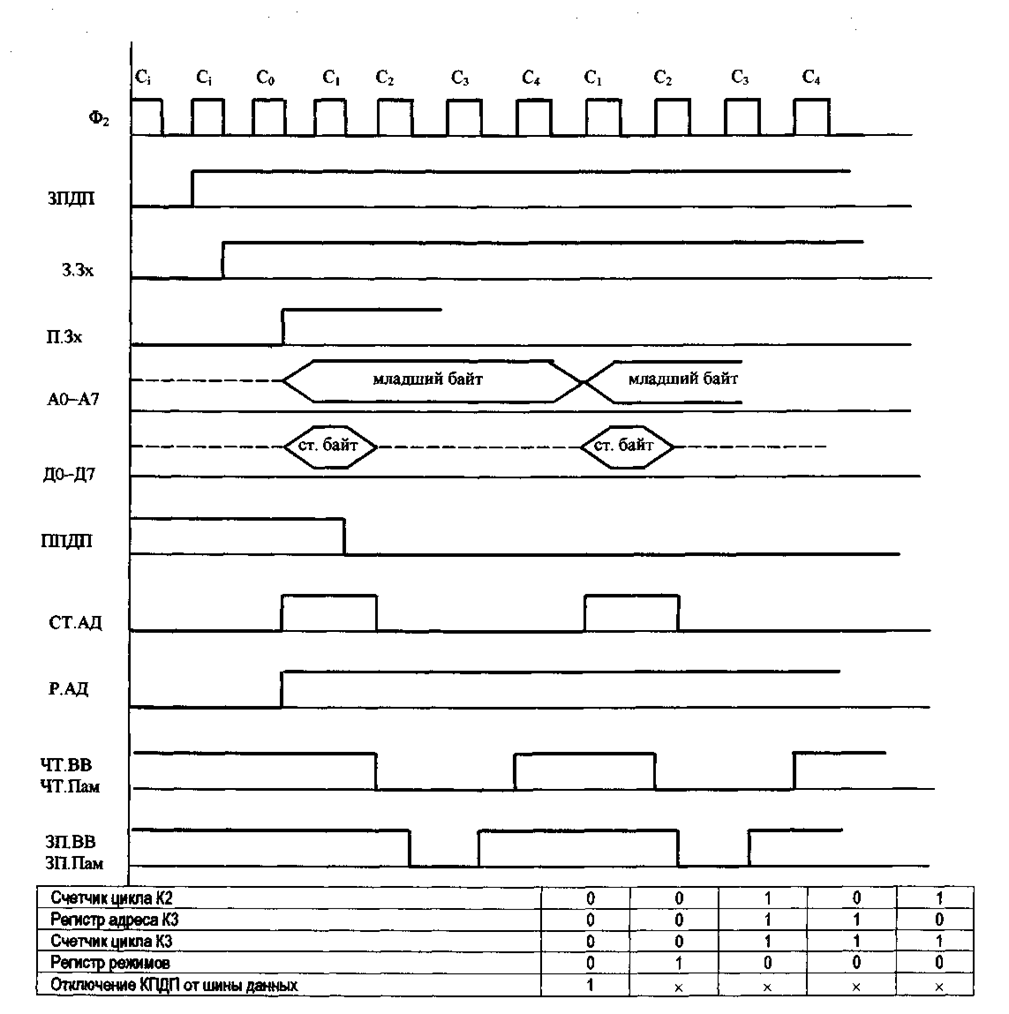

Формат регистра состояния:

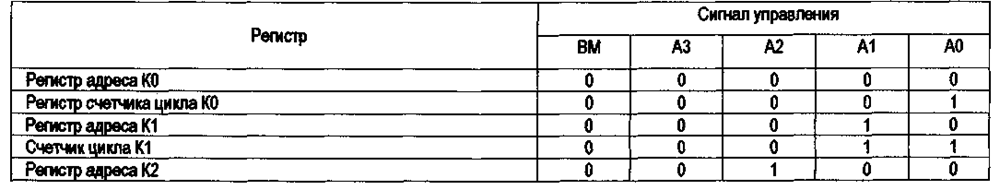

Таким образом, КПДП можно контролировать чтением трех регистров: регистра адреса, регистра счетчика циклов и 8-разрядного регистра режима для всех каналов. Чтение осуществляется командой IN В2, где В2 - второй бит команды. При чтении 16-разрядных регистров используются две команды IN с одним и тем же адресом, при этом считывается сначала младший байт, потом старший.

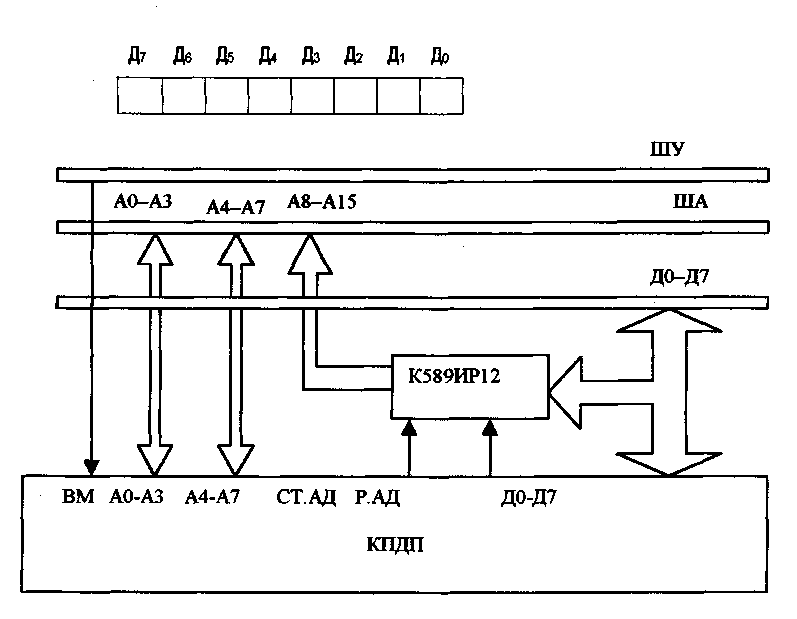

Схема

подключения КПДП к системной шине с использованием многорежимного буферного

регистра К589ИР12 (МБР)

изображена на рис. .

Для обращения к внутренним регистрам контроллера используются следующие адреса:

Работу КПДП поясняют временные диаграммы основных сигналов.

Ф2 - вход тактовых импульсов.

В ЗПДП каналов КЗ-КО единица указывает на запрос от внешнего устройства.

"1" на выходе З.Зх указывает на запрос о доступе КПДП к системным шинам.

"1" на П.Зх указывает на возможность доступа к системным шинам (доступ разрешен)

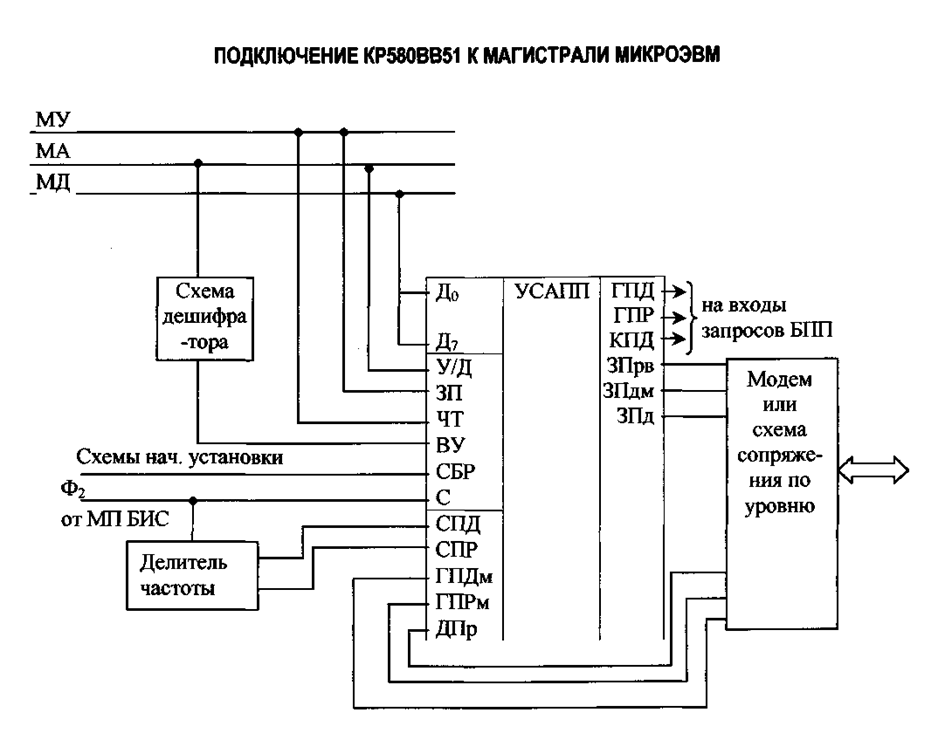

Делитель частоты обеспечивает деление тактовой последовательности d>2 до частоты, необходимой для работы передатчика или приемника. Выводы ГПД, ГПР подключаются ко входам запросов БПП. На вход СБР подается сигнал со схемы начальной установки МП БИС. Выход передатчика ДПД, вход приемника ДПр, сигналы запросов и подтверждение их готовности подключаются к модему или к схеме сопряжения по уровню, позволяющей осуществлять преобразование ТТЛ-уровней входных и выходных сигналов в уровни, необходимые для работы с внешними устройствами (дисплей и т.д.).

Автоматизированные системы контроля - подкласс информационной техники информационных управляющих вычислительных систем (ИУВС). В них необходимая информация об объекте контроля получается с помощью системы измерительных датчиков. В зависимости от характера использования ИУВС допускают два подхода к организации систем контроля:

1. в виде систем встроенного контроля конструктивно объединенных с блоками ИУВС;

2. в виде контрольной проверочной аппаратуры, которая конструктивно не объединяется с конкретной системой, а нужна для обслуживания группы ИУВС.

В зависимости от способа обработки информации различают аппаратный, программный и программно-логический методы контроля.

Аппаратный метод контроля предусматривает введение в структуру ИУВС оборудования, предназначенного для обнаружения ошибок при обработке и передаче информации.

1. Назначение и области применения микропроцессоров.

2. Классификация микропроцессорных устройств.

3. Архитектура микропроцессора.

4. Критерии выбора микропроцессора.

5. Архитектура КР580ИК80.

6. Входные и выходные сигналы КР580ИК80.

7. Машинный цикл, машинный такт, типы машинных циклов.

8. Запись слова состояния в регистр слова состояния (РгСС).

9. Назначение слова состояния.

10. Цикл извлечения кода команды из памяти.

11. Запись данных в память или внешнее устройство (ВУ).

12. Система команд, методы адресации данных.

13. Организация памяти в микропроцессорных устройствах.

14. Выполнение микропроцессором одно-, двух- и трехбайтных команд.

15. Организация устройств ввода-вывода информации.

16. Назначение программируемого параллельного интерфейса (ППИ) КР580ВВ55, его архитектура.

17. Входные и выходные сигналы ППИ КР580ВВ55.

18. Режимы работы ППИ КР580ВВ55.

19. Работа каналов А и В в режиме ввода данных (для ППИ КР580ВВ55).

20. Работа каналов А и В в режиме вывода данных (для ППИ КР580ВВ55).

21. Режим 2 работы ППИ КР580ВВ55.

22. Программирование ППИ КР580ВВ55.

23. Назначение блока приоритетного прерывания (БПП) КР580ВН59 и его устройство.

24. Входные и выходные сигналы БПП КР580ВН59.

25. Работа БПП КР580ВН59 при каскадном соединении.

26. Программирование БПП КР580ВН59, слова начальной установки.

27. Программирование БПП КР580ВН59, слова управления.

28. Режимы работы БПП КР580ВН59.

29. Организация прямого доступа к памяти микро-ЭВМ.

30. Назначение контроллера прямого доступа к памяти (КПДП) КР580ВТ57, его архитектура.

31. Входные и выходные сигналы КПДП КР580ВТ57.

32. Программирование КПДП КР580ВТ57, регистр адреса, регистр счетчика циклов.

33. Программирование КПДП КР580ВТ57, регистр режима.

34. Работа КПДП КР580ВТ57.

35. Характеристика 4-, 8-, 16-, 32-разрядных микропроцессоров, характеристика некоторых микропроцессорных комплектов.

36. Работа в режиме “захват” и при выполнении команды HALT для КР580ИК80.

37. Обслуживание запросов на прерывание, код прерывания и способы его задания.

38. Структуры МП систем.

39. Упрощенная схема ремиконт.

40. Обобщенная структура МПВУ.

41. Шинная организация микроЭВМ.

42. Принцип проектирования МП систем.

43. Обоснование выбора МП.

44. Контроль и диагностика МП систем.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.