ГЛАВА 5

ОПЕРАЦИИ С ШИНОЙ

Данная глава содержит сведения не обо всех операциях с шиной, производимых MC68020, а только о тех циклах обращения к пространству ЦП, без знания которых невозможно понимание ГЛАВЫ 6 РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА.

5.1 ЦИКЛЫ ОБРАЩЕНИЯ К ПРОСТРАНСТВУ ЦП

Обычные операции процессора с шиной можно разделить на две отдельных категории: циклы обращения к программному пространству и циклы обращения к пространству данных, различаемые по значению функционального кода, устанавливаемого на особых сигнальных линиях процессора (см. 4.1 ЛИНИИ ФУНКЦИОНАЛЬНОГО КОДА

(FC0...FC2)). Третий тип операций на шине включает те действия процессора, которые, строго говоря, не могут быть отнесены ни к одной из двух указанных категорий. Такие циклы называются циклами обращения к пространству ЦП (функциональный код = 111 ). К

этой категории относятся операции подтверждения прерывания, обработки точки останова, вызова модулей и связи с сопроцессором.

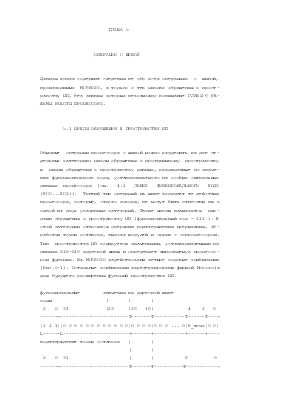

Тип пространства ЦП кодируется значениями, устанавливаемыми на линиях A16-A19 адресной шины и определяет выполняемую процессором функцию. На MC68020 задействованы четыре кодовые комбинации

(Рис.5-1). Остальные комбинации зарезервированы фирмой Motorola

для будущего расширения функций пространства ЦП.

функциональные значения на адресной шине коды | | |

2 0 31 |23 |19 16| 4 2 0

------¬------------------------T-------T-----------T------T---¬

¦1 1 1¦¦0 0 0 0 0 0 0 0 0 0 0 0¦0 0 0 0¦0 0 0 ... 0¦N_точк¦0 0¦

L------L-----------------------+-------+-----------+------+---подтверждение точки останова | |

| |

2 0 31 | | 6 0

------¬------------------------T-------T----------T-----------¬

¦1 1 1¦¦0 0 0 0 0 0 0 0 0 0 0 0¦0 0 0 1¦0 0 0 .. 0¦регистр MMU¦

L------L-----------------------+-------+----------+-----------управление уровнем доступа *) | |

| |

2 0 31 | |15 13 4 0

------¬------------------------T-------T-----T-----T----------¬

¦1 1 1¦¦0 0 0 0 0 0 0 0 0 0 0 0¦0 0 1 0¦ CPID¦0...0¦регистр СП¦

L------L-----------------------+-------+-----+-----+----------связь с сопроцессором

2 0 31 |19 16| 3 1 0

------¬------------------------T-------T------------T-------T-¬

¦1 1 1¦¦1 1 1 1 1 1 1 1 1 1 1 1¦1 1 1 1¦1 1 1 ... 1 ¦уровень¦1¦

L------L-----------------------+-------+------------+-------+-подтверждение прерывания ^ ^

L-поле -типа пространства ЦП

*) Подробности см. в ПРИЛОЖЕНИИ D СПЕЦИАЛЬНЫЕ ВОПРОСЫ.

Рис.5-1. Кодирование адресных пространств процессора MC68020

5.1.1 Действия по прерыванию

В данном разделе описывается процесс распознавания и подтверждения прерываний процессором MC68020. Подробно обработка прерываний описана в 6.3.10 Прерывания.

5.1.1.1 УРОВНИ ПРЕРЫВАНИЯ. Архитектура семейства M68000 допускает использование прерываний семи уровней приоритета (седьмой уровень - наивысший). Допускается подключение внешних устройств с одинаковым уровнем приоритета прерываний, так что ограничения на количество устройств, могущих вызвать прерывание работы процессора, отсутствуют. Распознавание и последующая обработка прерываний обусловлены значением кода, считываемого с управляющих линий IPL0-IPL2, а также значением текущего уровня приоритета процессора, задаваемым маской приоритета прерываний (I2,

I1, I0) в регистре состояния MC68020. Нулевой уровень запроса прерывания (IPL0/IPL1/IPL2=HHH) означает, что запросов на обслуживание прерываний нет. При запросе прерывания с приоритетом в диапазоне от 1 до 6 (осуществляемом установкой соответствующего кода на линиях IPL0-IPL2), процессор сравнивает уровень запрашиваемого прерывания с маской прерывания и определяет, надо ли обрабатывать этот запрос. Игнорируются все запросы, у которых уровень приоритета не превышает текущего приоритета процессора, определяемого маской прерывания. Прерывания седьмого уровня не маскируются, их обработка описана в 6.3.10 Прерывания.

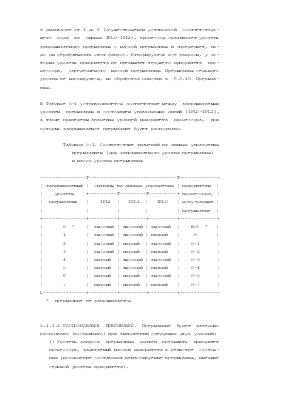

В Таблице 5-1 устанавливается соответствие между запрашиваемым уровнем прерывания и состоянием управляющих линий (IPL0-IPL2), а также приведены значения уровней приоритета процессора, при которых запрашиваемое прерывание будет распознано.

Таблица 5-1. Соответствие значений на линиях управления прерыванием (для запрашиваемого уровня прерывания)

и масок уровня прерывания

----------------T-------------------------------T-------------¬

¦ запрашиваемый ¦ сигналы на линиях управления ¦ приоритеты ¦

¦ уровень +----------T---------T----------+ процессора, ¦

¦ прерывания ¦ IPL2 ¦ IPL1 ¦ IPL0 ¦ допускающие ¦

¦ ¦ ¦ ¦ ¦ прерывание ¦

+---------------+----------+---------+----------+-------------+

¦ 0 * ¦ высокий ¦ высокий ¦ высокий ¦ Н/З * ¦

¦ 1 ¦ высокий ¦ высокий ¦ низкий ¦ 0 ¦

¦ 2 ¦ высокий ¦ низкий ¦ высокий ¦ 0-1 ¦

¦ 3 ¦ высокий ¦ низкий ¦ низкий ¦ 0-2 ¦

¦ 4 ¦ низкий ¦ высокий ¦ высокий ¦ 0-3 ¦

¦ 5 ¦ низкий ¦ высокий ¦ низкий ¦ 0-4 ¦

¦ 6 ¦ низкий ¦ низкий ¦ высокий ¦ 0-5 ¦

¦ 7 ¦ низкий ¦ низкий ¦ низкий ¦ 0-7 ¦

L---------------+----------+---------+----------+-------------* прерывание не запрашивается

5.1.1.2 РАСПОЗНАВАНИЕ ПРЕРЫВАНИЙ. Прерывание будет заведомо распознано (воспринято) при выполнении следующих двух условий:

1) Уровень запроса прерывания должен превышать приоритет процессора, задаваемый маской приоритета в регистре состояния (исключение составляют немаскируемые прерывания, имеющие седьмой уровень приоритета).

2) Установленный на линиях управления прерыванием IPL0-IPL2

код уровня запрашиваемого прерывания должен удерживаться до прихода подтверждения прерывания от MC68020 (см. 5.1.1.3

ПОСЛЕДОВАТЕЛЬНОСТЬ ПОДТВЕРЖДЕНИЯ ПРЕРЫВАНИЯ (IACK)).

Соблюдение этих правил гарантирует, что прерывание будет обработано; не исключается однако, что оно может быть обработано и в том случае, когда запрос на него будет снят до цикла IACK.

Для синхронизации и согласования сигналов опрос линий IPL0-IPL2

производится схемами синхронизации ввода MC68020 при прохождении последовательных задних фронтов тактирующих импульсов. Действительным считается запрос на прерывание, удерживаемый неизменным в течение двух последовательных тактов, поэтому процессором может быть воспринят запрос на прерывание, выставленный всего на два такта.

Прерывание, воспринятое процессором по описанной выше схеме, не влечет немедленной обработки, а откладывается. (Причем откладываются только прерывания, принятые к обработке т.е. те, приоритет которых выше текущего приоритета процессора.) После задержки на синхронизацию и согласование будет установлен сигнал

IPEND*, извещающий внешние устройства о том, что MC68020 имеет отложенное прерывание. Обработка исключения по отложенному прерыванию начнется непосредственно перед выполнением следующей команды, при отсутствии, разумеется, другого действительного прерывания с более высоким приоритетом. См. 4.7.2 Отложенное прерывание (IPEND*).

5.1.1.3 ПОСЛЕДОВАТЕЛЬНОСТЬ ПОДТВЕРЖДЕНИЯ ПРЕРЫВАНИЯ (IACK). В

случае, если имеется отложенное прерывание и отсутствуют отложенные исключения более высокого приоритета, то по завершении выполнения очередной команды процессор инициирует обработку этого прерывания (см. 6.2 ОБРАБОТКА ИСКЛЮЧЕНИЙ). Для правильного обслуживания прерывания необходимо в первую очередь определить начальный адрес соответствующей программы обработки. В

процессорах семейства M68000 получение необходимой для этого информации осуществляется в цикле подтверждения прерывания. В

ходе этого цикла процессором будет получен извне или самостоятельно сгенерирован номер вектора прерывания (см. 6.2.1 Векторы исключений).

В MC68020 предусмотрено два способа получения номера вектора прерывания. Устройства, имеющие векторный регистр, могут передавать вектор процессору по шине данных в цикле IACK. Для устройств, которые не могут передать вектор прерывания, MC68020

использует номера, автоматически генерируемые логическими схемами процессора. В обоих случаях со стороны MC68020 последовательность IACK одна и та же, разнятся только ответы устройства, запрашивающего прерывание.

В начале цикла IACK процессор устанавливает функциональный код

7, что указывает на обращение к пространству ЦП. Запрашиваемое значение приоритета воспроизводится на линиях A1-A3, а на остальных линиях шины адреса устанавливается единичный код, что идентифицирует данный цикл шины как цикл подтверждения прерывания. Далее устройство, запросившее прерывание, должно либо поместить номер вектора прерывания в младший байт своего порта данных и указать размер порта установкой соответствующих значений на линиях DSACK0*-DSACK1*, либо установить сигнал AVEC*, извещая процессор о том, что тот должен сам выбрать вектор прерывания в соответствии с запрашиваемым уровнем приоритета прерывания.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.