Поддерживаются целочисленные типы :

байт

полуслово (два байта) – должно в памяти быть выровнено по

четному адресу

слово (четыре байта) – должно в памяти быть выровнено по

адресу, кратному 4.

При загрузке байта или полуслова (пересылке из памяти в регистр) происходит автоматическое расширение старшей части, поэтому различаются беззнаковые операнды (расширение нулями) и знаковые (расширение знакового разряда).

С точки зрения программиста, процессор может находиться в двух состояниях:

Состояние ARM. В нем все команды имеют длину 4 байта и выровнены по адресам, кратным 4.

Состояние Thumb. В нем команды имеют длину 2 байта и выровнены по адресам, кратным 2. Набор команд в состоянии Thumb функционально является подмножеством набора команд в режиме ARM. Переход из одного состояния в другое [apn1] возможен почти в любой момент, при этом сохраняется режим работы и содержимое регистров.

Режимов работы ‑ семь.

User (usr): Обычный пользовательский режим работы.

FIQ (fiq): Режим «быстрого» прерывания. Designed to support a data transfer or channel process

IRQ (irq): Режим «обычного» прерывания. Used for general-purpose interrupt handling

Supervisor (svc): Защищенный режим для операционной системы. Protected mode for the operating system

Abort mode (abt): Режим обработки исключения, возникшего при доступе к операнду. Entered after a data or instruction prefetch abort

System (sys): Привилегированный A privileged user mode for the operating system

Undefined (und): Entered when an undefined instruction is executed

Содержит набор регистров общего назначения РОН.

Регистры R0…R7 существуют в единственном экземпляре, т.е. имена R0…R7 соответствуют одному набору физических регистров, независимо от режима.

Каждый из регистров R8…R14 реализованы в нескольких копиях, наборах (банках), соответствующих разным режимам. Это означает, что в резных режимах одни и те же имена ссылаются на различные физические регистры.

Регистр R15 это счетчик команд PC (Program Counter).

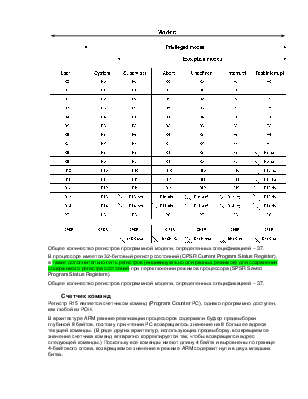

Вышеприведенная таблица показывает, как распределены регистры по «банкам» (заштрихованный угол означает, что данный регистр в данном режиме реализован в отдельном банке).

Регистры R8…R12 реализованы в двух банках. Один используется во всех режимах, кроме FIQ (Fast Interrupt), в то время, как второй банк – в режиме FIQ. Это позволяет быстро (не затрачивая времени на сохранение-восстановление контекста) выполнять короткие обработчики прерывания.

R13 и R14 реализованы в шести банках. Регистр R13 используется как указатель стека SP. Это является только соглашением, так как в архитектуре ARM нет ни специальных команд обращения к стеку, ни каких-либо аппаратно реализованных функциональностей, использующих R13 для стекового доступа. Однако такие команды есть в 16-битовом режиме (Thumb).

Регистр R14, иначе называемый регистром связи (Link Register LR), выполняет две специальные функции:

При обращении к подпрограмме в LR сохраняется адрес возврата из ПП (в каждом из режимов используется свой экземпляр LR). Возврат из ПП производится копированием содержимого LR в счетчик команд PC.

При входе в прерывание адрес возврата также сохраняется в LR. Возврат из обработчика происходит подобно возврату из подпрограммы, однако с некоторыми отличиями.

Общее

количество регистров программной модели, определенных спецификацией – 37.

Общее

количество регистров программной модели, определенных спецификацией – 37.

В процессоре имеется 32-битовый регистр состояний (CPSR Current Program Status Register), а также дополнительно пять регистров (индивидуально для разных режимов) для сохранения содержимого регистра состояний при переключении режимов процессора (SPSR Saved Program Status Registers).

Общее количество регистров программной модели, определенных спецификацией – 37.

Регистр R15 является счетчиком команд (Program Counter PC), однако программно доступен, как любой из РОН.

В архитектуре ARM ранние реализации процессоров содержали буфер предвыборки глубиной 8 байтов, поэтому при чтении PC возвращалось значение на 8 большее адреса текущей команды. (В ряде других архитектур, использующих предвыборку, возвращаемое значение счетчика команд аппаратно корректируется так, чтобы возвращался адрес следующей команды.) Поскольку все команды имеют длину 4 байта и выровнены по границе 4-байтового слова, возвращаемое значение в режиме ARM содержит нули в двух младших битах.

Спецификация предусматривает, что в реализациях, имеющих большую, нежели 8 байтов, глубину предвыборки, возвращаемое значение должно быть на 8 больше адреса текущей команды.

Запись в счетчик команд эквивалента команде безусловного перехода. Записываемая величина должна быть кратна 4. Так, например, возврат из подпрограммы осуществляется копированием LR в PC.

N – флаг знака

Z – флаг нуля

C –флаг переноса

V –флаг переполнения

Q – индицирует переполнение или насыщение при выполнении DSP-команд расширенного набора.

CPSW – Curent Program Status Word – текущее значение регистра состояния.

SRSW – Saved Program Status Word –сохраненные значения РСП для разных режимов работы.

Управляющие биты

I – маска запрета прерывания

F – маска запрета прерывания FIQ

T – флаг переключения режимов ARM (0) ‑ Thumb (1)

M4…M0 – биты режимов. Интерпретация их значений дана в таблице

Все режимы кроме User именуются привилегированными.

В состоянии ARM программисту видны 16 регистров общего назначения, а также один или два статусный

В архитектуре ARM реализован вывод-вывод, отображаемый на память. Это значит, что объекты (регистры) периферийных устройств РПУ видны программисту так же, как ячейки памяти, и для действий с содержимым РПУ можно использовать весь набор команд.

Его размер составляет 232байтов от 0 до 232-1, т.е. адрес рассматривается как число без знака. Объекты длиннее 1 МАЕ (длиной 2 либо 4 байта) должны быть выровнены по соответствующим границам, кратным длине объекта. Это означает, что адрес 2-байтового объекта содержит ноль в младшем бите, адрес 4-байтового объекта содержит ноль в двух младших битах.

Операции с адресами выполняются с использованием «обычных» целочисленных команд, т.е они дают результат по модулю 232. Однако, с учетом последующего расширения адресного пространства, не следует писать программы, которые явно используют это свойство.

Endiannes не фиксирован, могут быть как реализации little-endian, так и big-endian, так и смешанные (с переключением). Переключение (если оно есть) производится аппаратно (внешним сигналом) а не командами.

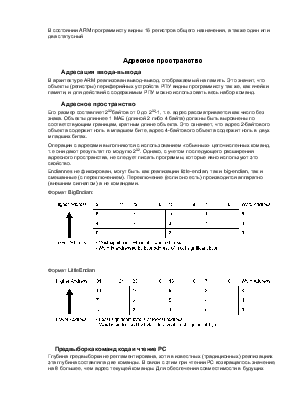

Формат BigEndian:

Формат LittleEndian

Глубина предвыборки не регламентирована, хотя в известных (традиционных) реализациях эта глубина составляла две команды. В связи с этим при чтении PC возвращалось значение, на 8 большее, чем адрес текущей команды. Для обеспечения совместимости в будущих реализациях с большей (либо меньшей, что вряд ли) глубиной предвыборки, при чтении PC будет обеспечен возврат значения на 8 превышающего адрес текущей команды.

В данном примере команда SUB программно заменяется на ADD. Поскольку к моменту замены SUB уже находится в буфере предвыборки, она и будет выполнена. ADD выполнится лишь при следующем проходе этого кода. Но если после выполнения STR произойдет прерывание, которое сбросит буфер предвыборки, то будет выполнена ADD.

LDR r0, AddInstr

STR r0, NextInstr

NwxtInstr

SUB r1, r1, #1

…

…

AddInstr

ADD r1, r1, #1

Отметим, что в архитектуре х86 аппаратно обеспечивается, что, даже если данная команда К1 модифицирует следующую команду К2 (которая находится в буфере предвыборки, и, возможно, уже декодирована и начала исполняться), то будет исполнена модифицированная версия команды К2 (т.е. буфер предвыборки и все прочие выполненные этапы К2 будут аннулированы, и выполнение К2 начнется заново).

Спецификация архитектуры допускает варианты реализации, различие которых не гарантирует, что самомодифицируемый код будет надежно (одинаково) выполняться на разных реализациях. Поэтому следует избегать использования самомодифицируемого кода.

Однако совокупность «операционная система – запускаемая программа» выполняет последовательность «загрузка кода – передача ему управления», и поэтому, строго говоря, также является процессом с самомодификацией.

Для каждой реализации архитектуры ARM определены так называемые IMB (Instruction Memory Barrier) – последовательности, которые должны выполняться после модификации, но до передачи управления коду. В противном случае результат может быть непредсказуемым. IMB рекомендуется реализовывать в виде системных функций, которые вызываются программными прерываниями.

Основное отличие при обращении к адресам, соответствующим портам ввода-вывода, состоит в том, что два последовательных чтения могут возвратить разные значения (например, чтение из порта, связанного с FIFO).

Могут возникнуть проблемы, связанные с использованием кэширования или буферизации для адресов ввода-выводат. Поэтому порты ввода-вывода обычно располагают в участках адресного пространства, которые отмечают как некэшируемые.

[apn1] АРМ7-28

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.