1) Запрос ПДП выдает

ВНУ на вход КПДП

2) Разрешение приритетов, если запросов много делает

КПДП

3) Формирование запроса в процессор делает КПДП

4) Передача управления каналом контроллеру ПДП делает

процессор

5) Формирование управляющих сигналов и адресов в канал

и сигнала подтверждения запроса ПДП в ВНУ делает

КПДП

6) Формирование слов данных на шину данных канала делает ВНУ в

ответ на каждый сигнал

подтверждения запроса

7) Формирование запроса на регенерацию делает

КПДП каждые 15 мкс

8) Подсчет числа переданных слов делает

КПДП

9) Формирование сигнала окончания передачи делает

КПДП, в ответ на него –

10) Снятие сигнала запроса ПДП по окончании передачи должен сделать

ВНУ

Их различается три, по характеру реакции на сигнал запроса, поступающий от ВНУ.

1) Одиночная передача – на каждый фронт сигнала запроса передается одно слово данных

2) Передача по запросу - после подачи сигнала запроса передача продолжается до тех пор, пока сигнал запроса активен, и прекращается, если ВНУ снимает сигнал запроса, хотя передача и не завершена (т.е. не передано количество слов, указанное при программировании КПДП

3) Блочная передача – после подачи сигнала запроса передаются все запрошенные слова, независимо от дальнейшего поведения сигнала запроса.

Что (какая схемотехника) должно содержаться в устройстве, чтобы оно могло быть подключено к магистрали и обеспечивать обмен (при разных режимах: по опросу, по прерыванию, ПДП)

и переключение режима их работы (со входа на выход и обратно)

выходных линий, потребление тока по входным линиям.

одних и тех же линий несколькими устройствами

(МГ стр.421) Два разъема, содержащие соответственно 62 (разъем XT) и 36 контактов.

На разъемах имеются линии для четырех питающих напряжений ±5 В и ±12 В. Токи потребления плат расширения, вставляемые в разъемы шины ISA, не должны превышать следующих значений:

|

Напряжение |

+5 В |

-5 В |

+12 В |

-12 В |

|

|

Допустимые токи, А |

Для 8-разрядной платы (XT) |

3 |

? |

1,5 |

? |

|

Для 16-разрядной платы (AT) |

4,5 |

? |

1,5 |

? |

|

|

Суммарный для источника 200Вт |

19,8 |

0,3 |

7,3 |

0,3 |

Магистраль PCI local bus (Peripheral Component Interconnect)

PCI это локальная шина, так как она занимает место между шиной процессора и периферийной шиной (например ISA). В отличие от ISA , шина PCI четко стандартизована. В настоящее время действует спецификация шины PCI ver.2.1.

В отличие от магистрали ISA, в которой управление магистралью поддерживается схемотехникой, сосредоточенной в устройствах-абонентах, магистраль PCI управляется индивидуальным контроллером, который имеет свою систему управляющих команд, и одной из основных функций которого является конфигурирование устройств, включенных в магистраль. Каждое устройство, включаемое в PCI, должно поддерживать возможности автоматической конфигурации.

На магистрали предусматривается отдельное адресное пространство для портов ввода-вывода.

Соответствует разрядности 32-битовой шины адреса и равен 232 = 4 Гбайт. В стандарте предусмотрен вариант 64-разрядной шины адреса, т.е. возможна адресация с использованием 64-разрядного адреса. Реализация шины в PC-совместимых компьютерах не поддерживает 64-битовую адресацию.

Периферийные устройства могу использовать адресное пространство памяти так же как и адресное пространство ввода-вывода.

232=4 Гбайт или 264»6,4*1019 адресов. Одно физическое/логическое устройство обычно занимает в адресном пространстве ввода-вывода более чем один адрес (некоторые могут занимать 32…64 адреса).

Может быть (в соответствии со спецификацией ver.2.1) 32 или 64 разряда.

адреса-данных использовано как в 32 так и в 64-разрядном варианте. Адрес и данные передаются по одним и тем же линиям в разные моменты времени.

шины IPC по спецификации 2.1 равна 33 или 66 МГц (т.е. один такт – 30 или15 нс). В PC-совместимых машинах используется 33 МГц. (В то же время частота внутренней системной шины, связывающей процессор с подсистемой оперативной памяти, может достигать 100 МГц)

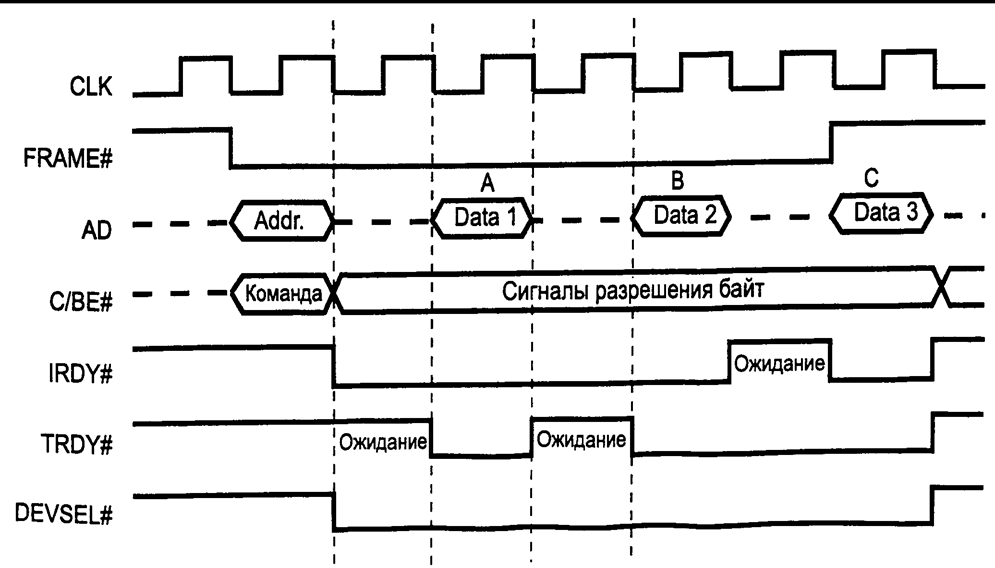

В шине PCI нет понятия фиксированного канального цикла.– в описании вместо понятия «канальный цикл» используется понятие «транзакция». Все транзакции трактуются как пакетные: в начале транзакции идет фаза адреса (длительностью в один такт), после чего следуют одна или несколько фаз данных. Длительность фазы данных минимально также один такт, но как Master (Initiator) так и Slave (Target) могут в каждой фазе данных вводить такты ожидания (подряд не более семи). Таким образом, максимальная скорость передачи приближается к одному слову за такт. А минимальная скорость обмена составляет 8 тактов/слово, т.е. около 4 слов/мкс. (Если устройство не в состоянии поддерживать такую скорость, обмен возможен только одиночными словами ???)

.Заимствована из книги М. Гук.Аппаратные средства IBM PC. Энциклопедия – СПб: Питер Ком, 1998, стр.437.

.

Порядок обмена:

1) Инициатор активирует сигнал FRAME# (кадр), отмечающий начало и конец транзакции и одновременно по шине AD передает адрес, а по линиям C/BE# - тип транзакции (команду)

2) Адресованое целевое устройство отвечает сигналом (Device Select – устройство выбрано)

3) Инициатор сигналом IRDY# (Initiator Ready - готовность инициатора) и независимо от него целевое устройство сигналом TRDY# (Target Ready – готовность целевого устройства) подтверждают свою готовность к обмену.

4) Обмен данными происходит в каждом такте только при условии наличия обоих сигналов, упомянутых в п.3). Если какое-либо из устройств «не успевает», оно может снять свой сигнал готовности, в результате чего вводятся такты ожидания (не более 7 тактов между соседними тактами данных), до тех пор, пока оба сигнала готовности вновь не станут активными.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.