VIII. ШИННЫЕ ЦИКЛЫ И КОНВЕЙЕРНАЯ ОБРАБОТКА

КОМАНД

1. Шинные циклы процессора

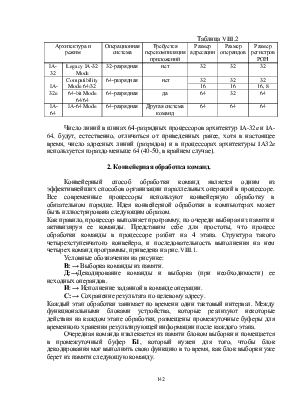

Напомним что задача, которая должна быть выполнена компьютером, представляется ему в виде программы. Программа состоит из определенной последовательности инструкций или команд. Команды программы кодируются двоичными словами и размещаются в памяти компьютера. Основной целью функционирования компьютера является последовательное извлечение из памяти и выполнение команд программы.

Выполнение операции по извлечению из памяти и выполнению одной команды, а также и интервал времени, требующийся для этого, носит название командного цикла.

За время одного командного цикла процессор может обращаться к памяти, или периферийным устройствам, несколько раз, поскольку кроме выборки самой команды, в командном цикле может потребоваться выборка операндов и запоминание результата.

Однократный обмен информацией между процессором и памятью, или процессором и периферийным устройством носит название машинного цикла (цикла шины)или цикла магистрали.

Таким образом, командный цикл процессора состоит из одного или нескольких машинных циклов. Машинный цикл, в свою очередь, реализуется за один или несколько тактов (тактовых интервалов) – периодов частоты синхронизации тактового генератора микропроцессора.

В общем случае, обмен информацией между процессором семейства Х86 и другими устройствами системы обработки информации осуществляется при помощи трех основных шин:

· Двунаправленной 32 – разрядной (или 64 разрядной для процессоров Pentium +) шины данных – DB – (Data Bus);

· Шины адреса (в процессорах i386, i486 и Pentium – 30 двунаправленных линий А31…А2 и 4 однонаправленных линии выбора байтов BE3…BE0, а в процессорах Pentium Pro + - 33 двунаправленные линии А35…А3 и 8 однонаправленных линий выбора байтов BE7…BE0) – AB – (Address Bus);

· Шины управления с одно – и двунаправленными сигнальными и управляющими линиями – CB (Control Bus).

Совокупность этих трех шин иногда называют магистралью.

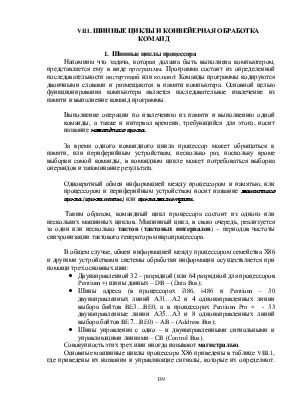

Основные машинные циклы процессора Х86 приведены в таблице VIII.1, где приведены их названия и управляющие сигналы, которые их определяют. Напомним, что символ # в конце обозначения сигнала указывает, что активным является низкий уровень этого сигнала. Отсутствие этого символа указывает на то, что данный сигнал активен при высоком уровне.

Таблица VIII.1

|

M/IO# |

D/C# |

W/R# |

Тип шинного цикла |

|

0 |

0 |

0 |

Подтверждение прерывания |

|

0 |

0 |

1 |

Останов / специальный цикл |

|

0 |

1 |

0 |

Чтение из устройства ввода/вывода |

|

0 |

1 |

1 |

Запись в устройство ввода/вывода |

|

1 |

0 |

0 |

Чтение команды из памяти |

|

1 |

0 |

1 |

Зарезервировано |

|

1 |

1 |

0 |

Чтение данных из памяти |

|

1 |

1 |

1 |

Запись данных в память |

При этом управляющий сигнал W/R# разделяет циклы записи и циклы чтения; сигнал D/C# разделяет циклы данных и циклы управления, а сигнал M/IO# разделяет циклы обращения к памяти и циклы обращения к устройствам ввода/вывода.

Кроме указанных основных циклов процессора, в нем имеются еще несколько специальных циклов, которые определяются специальными дополнительными сигналами на других специализированных выводах. Так, например, низкий уровень сигнала на выводе LOCK# задает цикл процессора типа чтение-модификация-запись, во время которого между чтением и записью процессор не может освободить магистраль (блокирует ее). Таким образом, при активизированном сигнале LOCK#, текущий цикл шины блокирован и процессору предоставлено исключительное право управления системной магистралью (при многопроцессорной работе на одной магистрали это особенно важно).

В дополнение отметим, что указанные выше характеристики шин характерны для процессоров архитектуры IA-32.

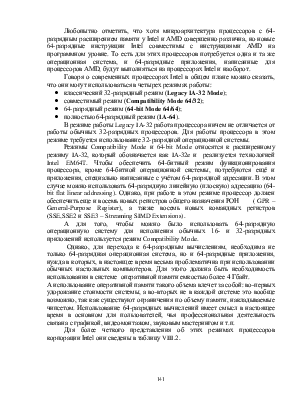

Однако большинство современных процессоров как корпорации Intel так и AMD (за исключением мобильных процессоров) поддерживают также 64-разрядную архитектуру расширения памяти. У AMD эта архитектура получила наименование архитектуры Х86-64 (2002 г.), а у Intel такая технология была названа Intel Extended Memory Technology (Intel EM64T) (2005 г.). При этом не следует путать технологию 64-разрядного расширения памяти с уже давно существующей технологией IA-64 (2001 г.), которая используется в истинно 64-разрядных процессорах Intel Itanium. При архитектуре IA-64 используются не только возможность 64-разрядного расширения адресов, но и возможность оперировать 64-разрядными данными.

Любопытно отметить, что хотя микроархитектура процессоров с 64-разрядным расширением памяти у Intel и AMD совершенно различна, но новые 64-разрядные инструкции Intel совместимы с инструкциями AMD на программном уровне. То есть для этих процессоров потребуется одна и та же операционная система, и 64-разрядные приложения, написанные для процессоров AMD, будут выполняться на процессорах Intel и наоборот.

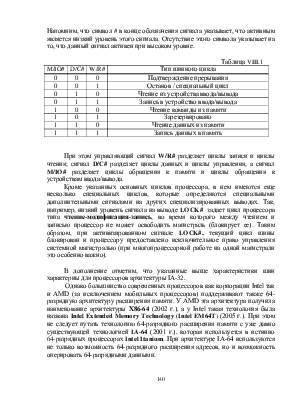

Говоря о современных процессорах Intel в общем плане можно сказать, что они могут использоваться в четырех режимах работы:

· классический 32-разрядный режим (Legacy IA-32 Mode);

· совместимый режим (Compatibility Mode 64/32);

· 64-разрядный режим (64-bitMode 64/64);

· полностью 64-разрядный режим (IA-64).

В режиме работы Legacy IA-32 работа процессора ничем не отличается от работы обычных 32-разрядных процессоров. Для работы процессора в этом режиме требуется использование 32-разрядной операционной системы.

Режимы Compatibility Mode и 64-bit Mode относятся к расширенному режиму IA-32, который обозначается как IA-32e и реализуется технологией Intel EM64T. Чтобы обеспечить 64-битный режим функционирования процессора, кроме 64-битной операционной системы, потребуются ещё и приложения, специально написанные с учётом 64-разрядной адресации. В этом случае можно использовать 64-разрядную линейную (плоскую) адресацию (64-bit flat linear addressing). Однако, при работе в этом режиме процессор должен обеспечить еще и восемь новых регистров общего назначения РОН ( GPR – General-Purpose Register), а также восемь новых командных регистров (SSE,SSE2 и SSE3 – Streaming SIMD Extensions).

А для того, чтобы можно было использовать 64-разрядную операционную систему для исполнения обычных 16- и 32-разрядных приложений используется режим Compatibility Mode.

Однако, для перехода к 64-разрядным вычислениям, необходима не только 64-разрядная операционная система, но и 64-разрядные приложения, нужда в которых, в настоящее время весьма проблематична при использовании обычных настольных компьютеров. Для этого должна быть необходимость использования в системе оперативной памяти емкостью более 4 Гбайт.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.