НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ

УНИВЕРСИТЕТ

ФАКУЛЬТЕТ АВТОМАТИКИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

Кафедра Систем Сбора и Обработки Данных

Дисциплина «Моделирование»

ЛАБОРАТОРНАЯ РАБОТА № 3

Моделирование элементов цифровых устройств

Группа: АТ-23 Преподаватель: Студенты:Мартыко Н. Кухто А.В.

Переверзина Ю.

Вариант:

Новосибирск

2005

ЦЕЛЬ РАБОТЫ.

Получение практических навыков моделирования дискретных систем на примере элементов цифровых устройств: двоичных сумматоров, триггеров, комбинаторной логики, статической и динамической памяти, арифметико-логических операций и управляющих команд.

ЗАДАНИЕ 1.

Разработка моделей, позволяющих производить перевод натуральных десятичных чисел в двоичную систему счисления и обратно (N =8).

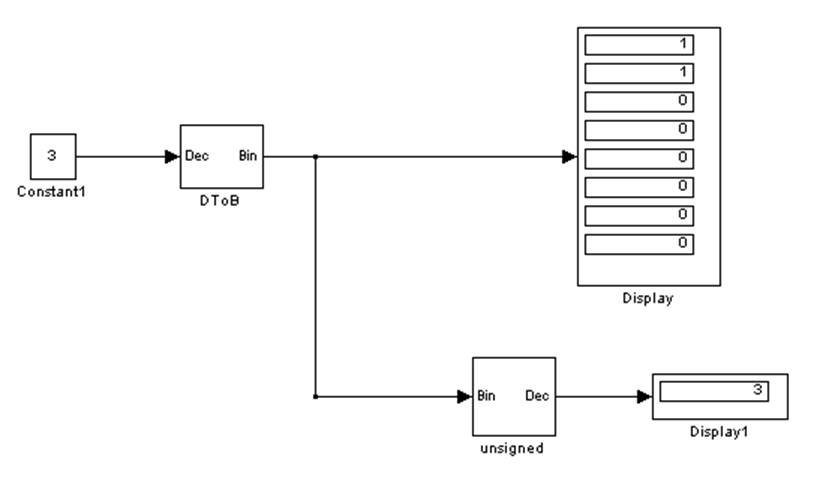

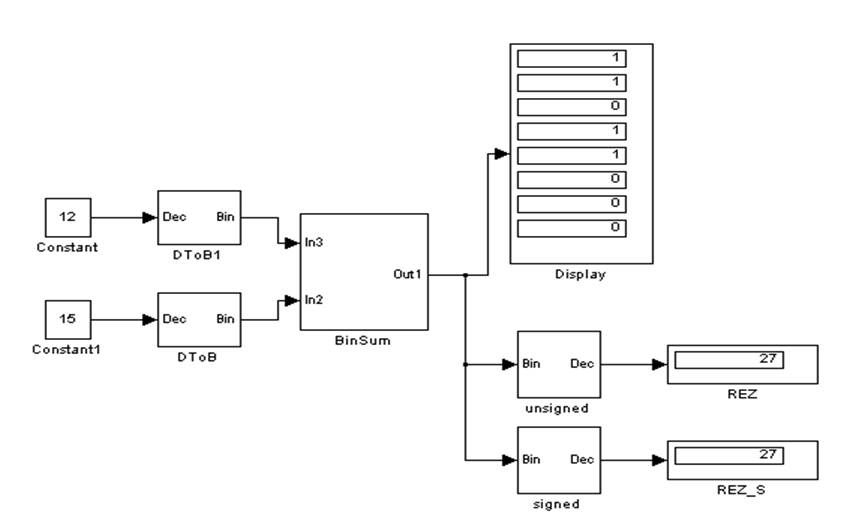

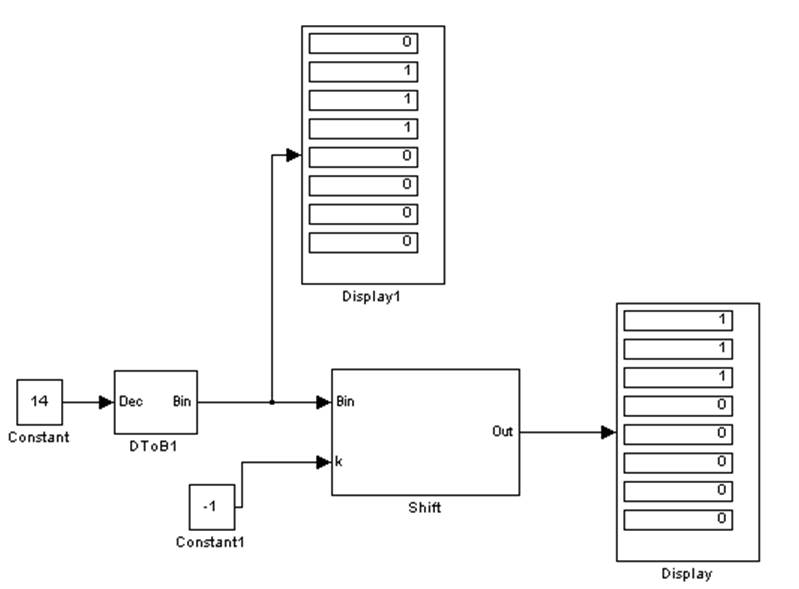

Рис. 1. Общий вид системы.

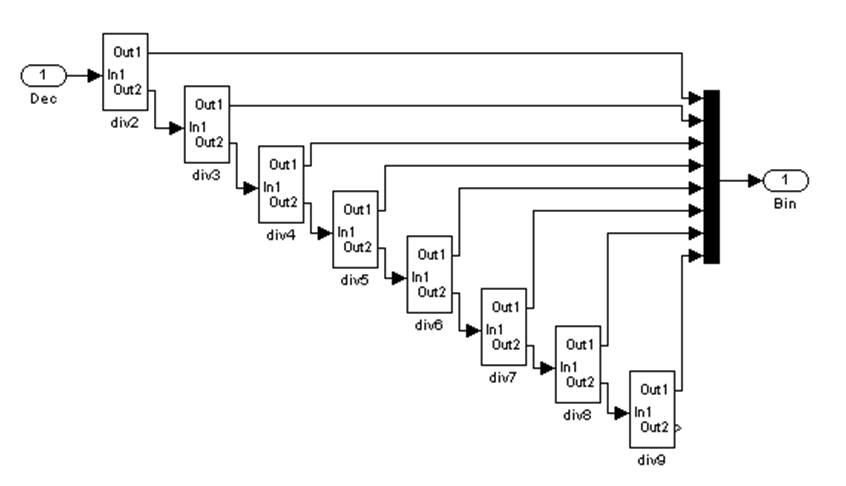

Рис. 2. Схема перевода из десятичной системы в двоичную (DToB).

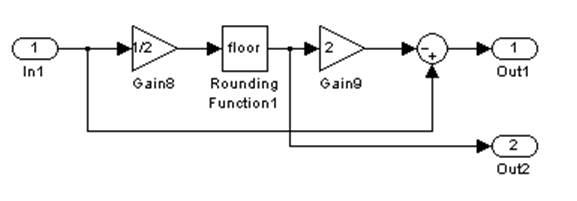

Рис. 3. Один из элементов деления на 2 (div2).

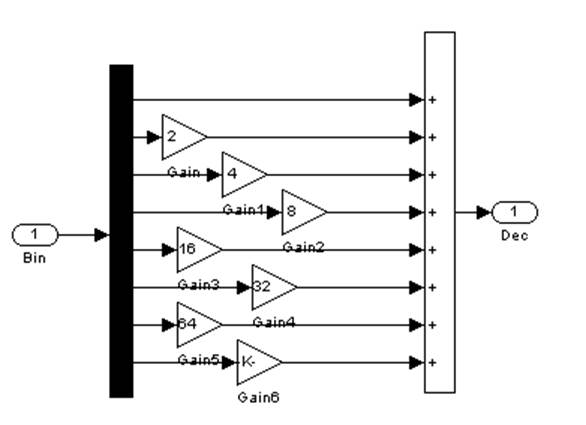

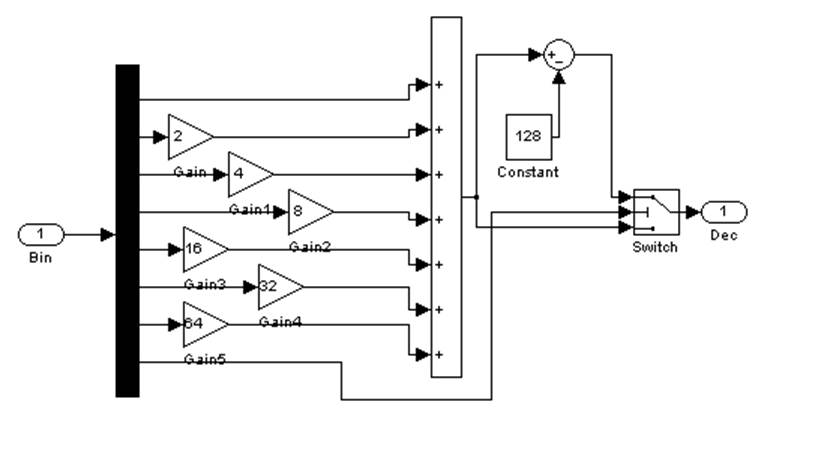

Рис. 4. Блок unsigned (перевод из двоичной системы в десятичную для беззнаковых чисел).

ЗАДАНИЕ 2.

Построение модели N-разрядного двоичного сумматора, используя средства комбинаторной логики или блоки логических операций. Сложение двух десятичных чисел с помощью разработанного сумматора.

Рис. 4. Общий вид модели двоичного сумматора.

Блоки DToB аналогичны блокам, используемым в предыдущем задании.

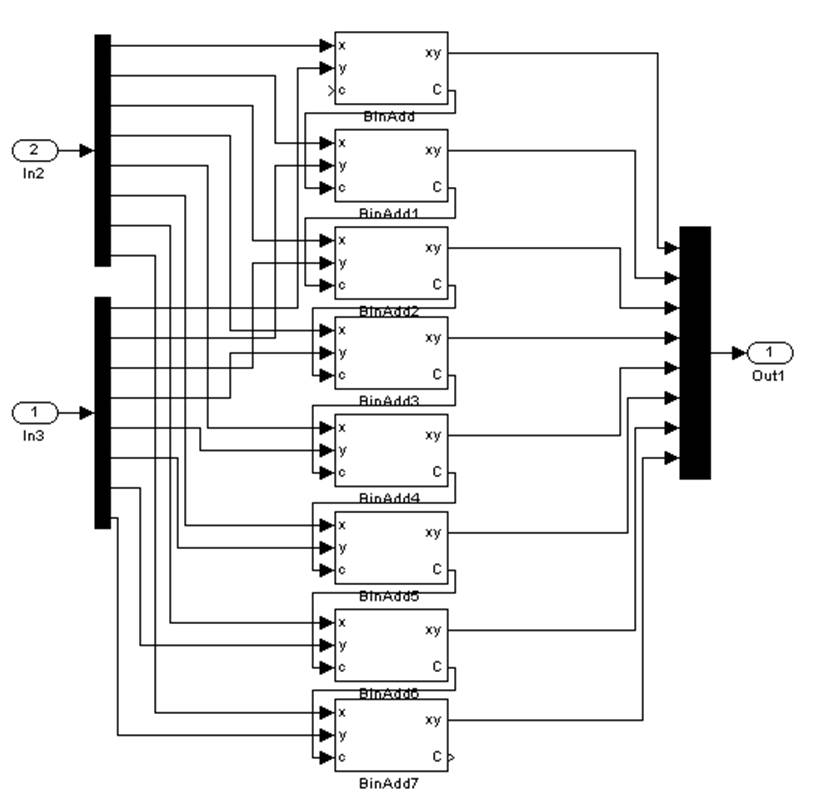

Рис. 5. Блок BinSum.

Блок BinSum построен на одноразрядных двоичных сумматорах (BinAdd), учитывающих переносы из младшего разряда и в старший разряд числа.

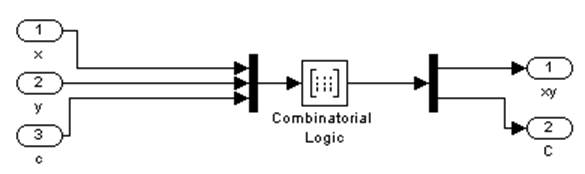

Рис. 6. Блок BinAdd.

Блок unsigned аналогичен соответствующему блоку в задании 1.

Рис. 7. Блок signed (для знаковых чисел).

ЗАДАНИЕ 3.

Дополните набор выполняемых команд операциями вычитания двух натуральных чисел (сложение в дополнительном коде), поразрядного сдвига влево и вправо.

Рис. 8. Общий вид модели, позволяющей производить поразрядный сдвиг вправо и влево.

Выбор направления сдвига осуществляется значением константы: “1” – сдвиг влево,

“-1” – сдвиг вправо.

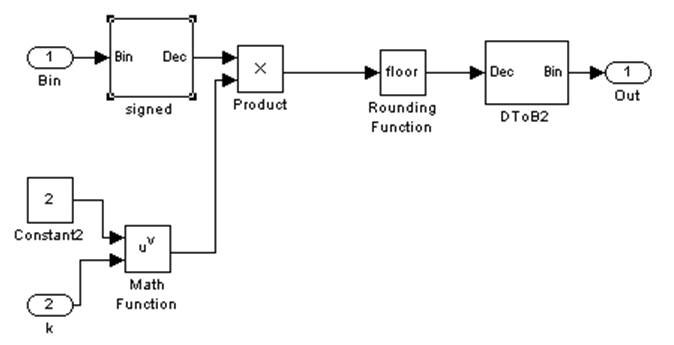

Рис. 9. Блок сдвига Shift.

ЗАДАНИЕ 4.

Разработать модель дешифратора на M входов, построенного с использованием моделей элементов И-НЕ и ИЛИ-НЕ.

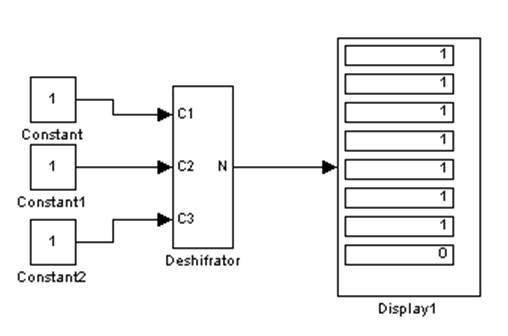

Рис. 10. Общий вид модели дешифратора.

Реализована модель 3-х входового полного дешифратора.

Он построен на элементах ИЛИ-НЕ.

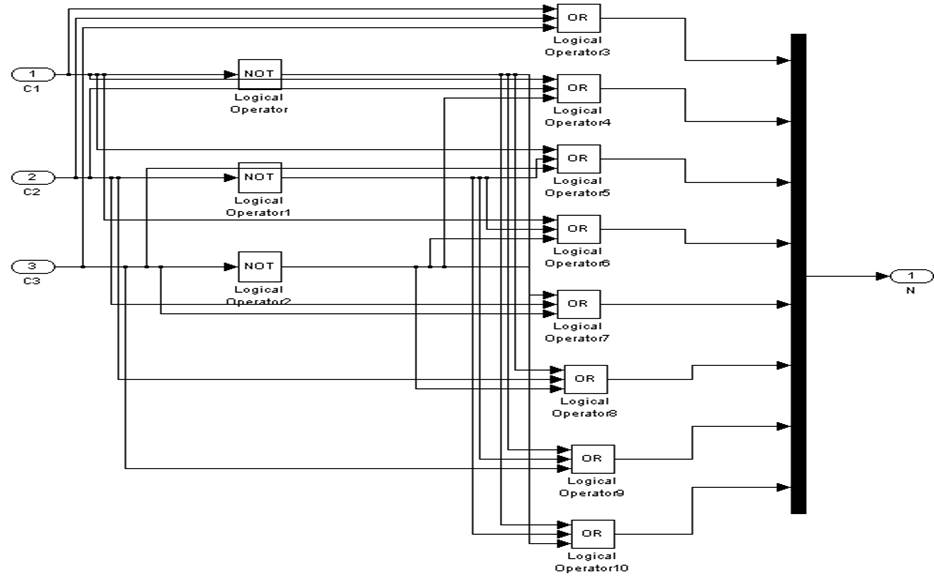

Рис. 11. Блок Deshifrator.

ЗАДАНИЕ 5.

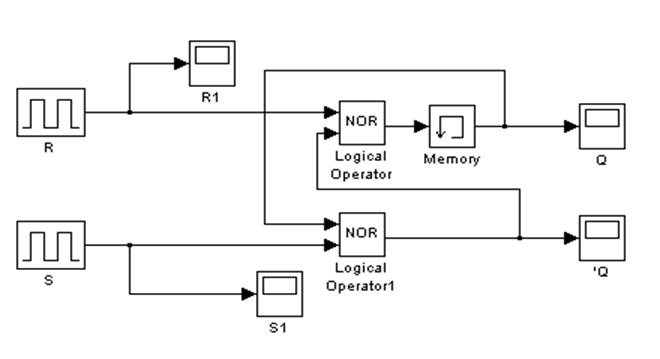

Разработать модель триггера. Для реализации модели используются элементы ИЛИ-НЕ.

Асинхронный RS-триггер.

Таблица переходов асинхронного RS-триггера

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

0 |

1 |

1 |

Установка 1 |

|

1 |

0 |

0 |

Установка 0 |

|

1 |

1 |

– |

Запрещено |

Рис. 12. Модель асинхронного RS-триггера.

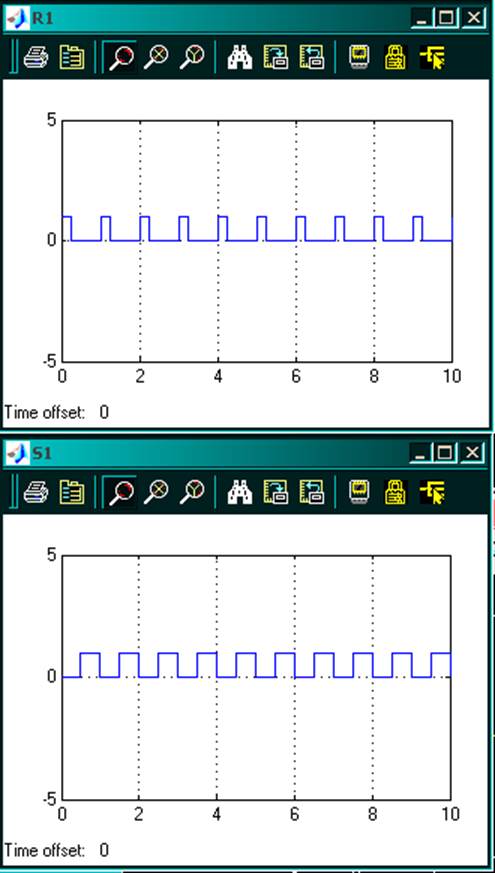

Рис. 13. Сигналы на входах триггера.

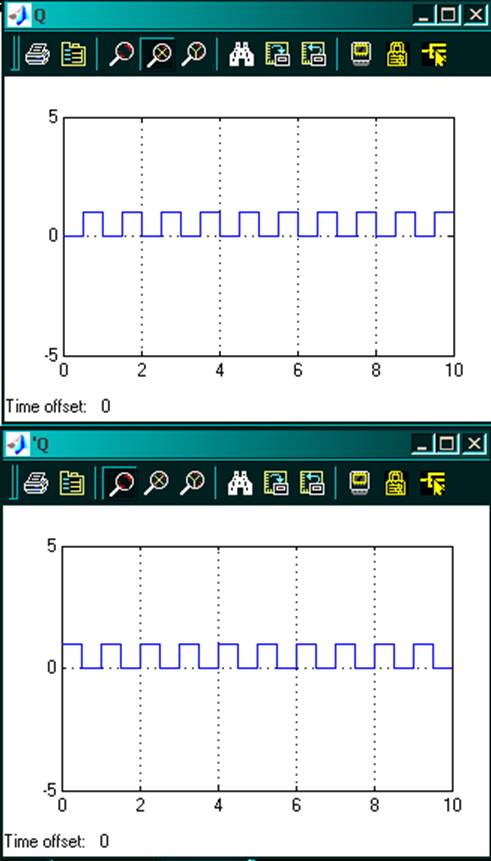

Рис. 14. Сигналы на выходах триггера.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.