VI. МЕТОДЫ ЗАЩИТЫ В ПРОЦЕССОРАХ СЕМЕЙСТВА Х86.

1. Общие сведения.

В современном мире компьютеры получили чрезвычайно широкое распространение и используются в очень важных и ответственных сферах применения. Они управляют сложнейшим информационным, технологическим и медицинским оборудованием, космическими объектами и атомными электростанциями, важнейшими оборонными объектами. Они используются для организации и ведения огромных баз данных и знаний и т.п. Человечество сейчас все больше и больше становится зависимым от компьютерных систем. Поэтому обеспечение надежности этих систем, причем таких систем, которые способны выполнять несколько задач одновременно, является важнейшей проблемой нашего времени. Надежность компьютерных систем в очень большой степени зависит от защиты информации, циркулирующей в них. Необходима защита операционной системы от воздействия пользовательских программ, от влияния периферийных устройств, через которые может произойти искажение программного обеспечения управляющего компьютера. При многозадачном режиме работы необходимо предусмотреть защиту каждой задачи друг от друга во избежание случайных или несанкционированных воздействий, могущих повлечь за собой их искажение и т.д.

Защита должна быть незаметна при нормальном функционировании компьютера, но при возникновении какого либо нарушения, например попытки выполнить сегмент данных вместо сегмента кода, она должна остановить процесс, и предоставить пользователю информацию о произошедшем нарушении с рекомендацией по его устранению, либо устранить его сама. Хорошо организованная защита должна обеспечить операционной системе возможность всегда сохранять управление.

В процессорах семейства Х86 все предусмотренные возможности защиты реализуются при переводе процессора в так называемый защищенный режим работы (ProtectedMode). Его еще именуют Protected VirtualAddressMode – защищенный режим виртуальной адресации, поскольку он позволяет реализовать виртуальную память объемом до 64 Тбайт для каждой задачи. Сам переход в защищенный режим осуществляется путем установки в единичное состояние бита PE (Protected Enable) в младшем байте управляющего регистра CR0.

Все используемые способы защиты памяти от ошибок пользователя, ряда сбоев в работе и несанкционированного доступа к информации, которые используются в современных персональных компьютерах на процессорах семейства Х86 можно разделить на две группы:

1) базовая или основная защита;

2) защита по привилегиям:

а) по привилегиям сегментов;

б) по привилегиям команд.

Как базовая защита, так и защита по привилегиям сегментов основаны на принципе сегментации памяти.

2. Базовая защита.

Средства базовой защиты включаются сразу же после переключения процессора в защищенный режим работы, независимо от того, включена ли страничная переадресация памяти, использован ли многозадачный режим работы или виртуальный режим. Основой базовой защиты является информация, закладываемая в дескрипторы сегментов и, в частности, в его байт прав доступа.

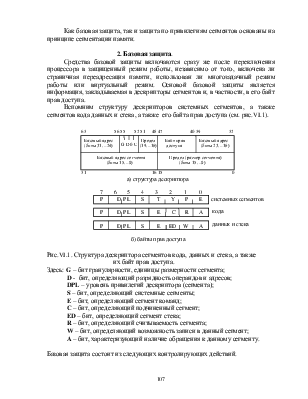

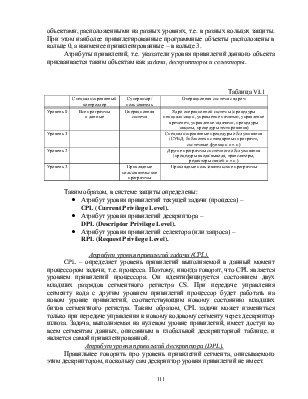

Вспомним структуру дескрипторов системных сегментов, а также сегментов кода данных и стека, а также его байта прав доступа (см. рис.VI.1).

Рис.VI.1. Структура дескриптора сегментов кода, данных и стека, а также

их байт прав доступа.

Здесь: G – бит гранулярности, единицы размерности сегмента;

D - бит, определяющий разрядность операндов и адресов;

DPL – уровень привилегий дескриптора (сегмента);

S– бит, определяющий системные сегменты;

E – бит, определяющий сегмент команд;

C – бит, определяющий подчиненный сегмент;

ED – бит, определяющий сегмент стека;

R– бит, определяющий считываемость сегмента;

W – бит, определяющий возможность записи в данный сегмент;

A – бит, характеризующий наличие обращения к данному сегменту.

Базовая защита состоит из следующих контролирующих действий.

Контроль адресации при обращении к памяти.

Контроль адресации при обращении к памяти в основном включает в себя следующие операции.

- Как только селектор, какого либо сегмента, поступает в соответствующий сегментный регистр, индекс селектора, умноженный на 8, сравнивается с пределом, приведенным в системном регистре GDTR. Этим самым контролируется реальная возможность нахождения искомого дескриптора в глобальной дескрипторной таблице.

- После выбора дескриптора соответствующего сегмента контролируется реальная возможность нахождения искомого адреса в данном сегменте путем сравнения смещения в сегменте (эффективного адреса), указанного в команде (инструкции), с пределом данного сегмента, приведенного в выбранном дескрипторе.

Если смещение в сегменте превышает предел, возникает особый случай (исключение), процессор уходит на прерывание и выполняет процедуру, обрабатывающую нарушение общей защиты. При этом, если бит ED в байте прав доступа равен 1, то процессор имеет дело с сегментом стека и, указанная процедура сравнения предела сегмента со смещением в сегменте неправомерна, Зато проверяется обязательная возможность записи в этот сегмент (W=1).

Контроль адресации только внутри запрашиваемого сегмента защищает соседние сегменты от нежелательных взаимодействий и искажений. Это особенно важно при многозадачном режиме работы, когда рядом в памяти могут быть размещены совершенно не связанные друг с другом сегменты.

Контроль исполняемости сегмента.

Исполняемый сегмент должен быть обязательно сегментом кода, в котором размещены исполняемые программы. Следовательно, и при первом вызове программного сегмента и при каждой передаче управления в программе необходима проверка состояния бита E в байте прав доступа. Он должен обязательно быть равен 1. Если же он равен 0, то это означает, что процессор имеет дело с сегментом данных или стека. Поэтому исполнение кода, содержащегося в нем, может привести к непредсказуемым последствиям, в том числе и к зависанию системы.

Контроль возможности копирования кодового сегмента.

В процессе создания программного обеспечения некоторые программы целесообразно защитить от нежелательного копирования. Поэтому каждое обращение к программному сегменту сопровождается проверкой бита R в байте прав доступа его дескриптора. Если значение этого бита равно 0, то это значит, что данный сегмент защищен от считывания и копирование его содержимого невозможно.

Контроль считываемости сегментов данных и стека.

Некоторые сегменты данных могут быть использованы для размещения каких-либо очень важных таблиц, констант, справочных данных, к которым можно обращаться только для считывания. Такие сегменты должны быть защищены как от случайной, так и от несанкционированной записи, которая может исказить содержимое этого справочного материала. Контроль запрета записи осуществляется по состоянию бита W в байте прав доступа. При W=0 запись в сегмент запрещена.

Контроль способа считываемости данных.

При вызове сегмента данных процессору необходимо, прежде всего, убедиться является ли этот сегмент сегментом данных или же он является сегментом стека. Если бит ED в байте прав доступа равен 0, то имеет место сегмент данных и данные должны считываться от младших адресов к старшим, начиная от базового адреса до адреса, равного сумме базового адреса и предела, указанного в дескрипторе. Если же ED=1, то имеет место сегмент стека и данные считываются от старших адресов к младшим, начиная от адреса, определяемого регистром указателя стека SP до значения предела.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.