Назначение выводов микросхемы: А-D-входы, Y0-Y9-выходы. Схема измерения дешифратора приведена на рис.2.3.

Рис.2.3. Схема измерения дешифратора

Для составления задания на моделирование следует согласно пунктам 1-10 раздела 2.1 ввести в графическом режиме схему измерения и установить параметры генераторов, к примеру, следующим образом:

Х1: ONTIME = OFFTIME = 1us;

Х2: ONTIME = OFFTIME = 2us;

Х3: ONTIME = OFFTIME = 4us;

Х4: ONTIME = OFFTIME = 8us.

Остальные параметры принимаются по умолчанию.

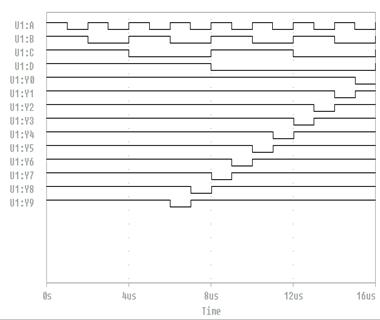

Далее согласно пп.11,12 раздела 2.3 следует установить время анализа равным не менее 16 us с шагом около 0,1 us и войти в графический постпроцессор Probe программы PSpice А_D. Там согласно п.13 раздела 2.3 выбрать входные и выходные узлы микросхемы и, выведя временные диаграммы (рис.2.4), используя указания п.13 раздела 2.1 снять таблицы переключения в виде табл.2.1.

Рис.2.4. Временные диаграммы сигналов дешифратора SN7442A

Таблица 2.1

Таблица истинности дешифратора 7442a

|

D |

C |

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.