Содержание

Техническое задание…………………………………………………………..…2

Анализ технического задания..……………………………………………….....3

Пределы изменения частоты сигнала на выходе.………………………….....4

Распределение адресного пространства….………………………………….....5

Описание принципиальной схемы…………..……………………………….....6

Программирование микросхем……………………………………………….....8

Программа……………………..………………………………………………...11

Перечень элементов микросхем……………………………………………......12

Таблица отсчетов.……………………………………………………………….13

Список использованных источников…………………………………………..15

Техническое задание

Разработать синтезатор сигналов в виде усеченной синусоиды с программно изменяемой частотой путем периодического считывания отсчетов с ЗУ на ЦАП с помощью контроллера ПДП.

Анализ технического задания

Для получения сигнала требуемой формы с помощью отсчетов можно воспользоваться табличным методом. При этом значения отсчетов хранятся в ПЗУ, один отсчет представлен одним байтом и значения сигнала изменяются в пределах 256 уровней, 128 отсчетов предназначено для представления изменения в пределах отрицательной полуволны синусоиды и 128 – в пределах положительной полуволны. Согласно техническому заданию отсчеты должны выводится на ЦАП в режиме ПДП. Для того чтобы воспроизводить сигнал нужной частоты запрос на переход в режим прямого доступа к памяти подается на контроллер ПДП с таймера. Таймер осуществляет деление входной частоты на константу пересчета, которая задается при программировании. Контроллер ПДП работает в режиме автоинициализации, тогда передача отсчетов ведется непрерывно.

Для создания микропроцессорной системы, решающей эту задачу потребуется:

1. Генератор тактовых импульсов.

2. Микропроцессорный блок (включает МП, регистр защелки адреса, двунаправленный буфер).

3. Таймер.

4. ПЗУ для хранения программы и отсчетов.

5. Контроллер ПДП, регистр.

6. Интерфейс ЦАП (регистр).

7. ЦАП.

Пределы изменения частоты сигнала на выходе

Частота

сигнала на выходе, полученного выбором определенного числа отсчетов за период

этого сигнала, определяется по формуле  ,

где

,

где

![]() – частота дискретизации,

– частота дискретизации, ![]() – число отсчетов за период.

– число отсчетов за период.

Число отсчетов за

период выбрано равным 800 для удобства расчетов. Частота дискретизации зависит

от константы пересчета таймера  , N – константа пересчета, которая изменяется в пределах от 0

до 9999,

, N – константа пересчета, которая изменяется в пределах от 0

до 9999, ![]() – тактовая частота генератора

импульсов с выхода CLK.

– тактовая частота генератора

импульсов с выхода CLK.

Максимальная частота дискретизации ограничивается временем необходимым для выдачи одного отсчета. Один отсчет передается в течение 4 тактов CLK , что составляет 4х250нс=1мс, следовательно, частота дискретизации не должна превышать 1 МГц (минимальное значение константы пересчета 4). Тогда частота сигнала равна 1250 Гц.

Минимальная

частота дискретизации может быть получена при константе пересчета 9999:  . При такой

частоте дискретизации на выходе может быть получен сигнал с частотой 0.5Гц.

. При такой

частоте дискретизации на выходе может быть получен сигнал с частотой 0.5Гц.

Таким образом, диапазон возможного изменения частоты составляет 0.5 – 1250 Гц.

Частота сигнала

на выходе может задаваться программно путем изменения константы пересчета  .

.

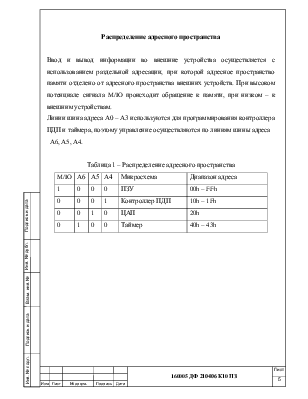

Распределение адресного пространства

Ввод и вывод информации во внешние устройства осуществляется с использованием раздельной адресации, при которой адресное пространство памяти отделено от адресного пространства внешних устройств. При высоком потенциале сигнала M/IO происходит обращение к памяти, при низком – к внешним устройствам.

Линии шина адреса А0 – А3 используются для программирования контроллера ПДП и таймера, поэтому управление осуществляются по линиям шины адреса

А6, А5, А4.

Таблица 1 – Распределение адресного пространства

|

M/IO |

А6 |

А5 |

А4 |

Микросхема |

Диапазон адреса |

|

1 |

0 |

0 |

0 |

ПЗУ |

00h – FFh |

|

0 |

0 |

0 |

1 |

Контроллер ПДП |

10h – 1Fh |

|

0 |

0 |

1 |

0 |

ЦАП |

20h |

|

0 |

1 |

0 |

0 |

Таймер |

40h – 43h |

Описание принципиальной схемы

1. Генератор тактовых импульсов КР1810ГФ84.

Формирует последовательность тактовых

импульсов и является задающим устройством для микропроцессора и периферийных

устройств. Включает схемы формирования тактовых импульсов (OSC, CLK, PCLK), сигнала сброса (RESET) и сигнала

готовности (READY). Сигнал RESET осуществляет начальную

установку микропроцессора, после поступления этого сигнала микропроцессор

прекращает работу и остается в режиме ожидания до окончания этого импульса.

Затем в течение 10 тактов происходит процесс инициализации, заключающийся в

обнулении сегментных регистров, регистра флагов и указателя команд. Схема

формирования тактовых импульсов вырабатывает сигналы: CLK – тактовая

частота для ЦП, PCLK – тактовая частота для управления периферийными БИС, OSC – тактовая

частота задающего генератора. Сигналы синхронны, их частоты связаны соотношением:

![]() .

Сигналы формируются из колебаний основной частоты кварцевого резонатора, подключаемого

к входам Х1, Х2.

.

Сигналы формируются из колебаний основной частоты кварцевого резонатора, подключаемого

к входам Х1, Х2.

2. Микропроцессор К1810ВМ88. Является 16 - разрядным, с 8-разрядной внешней магистралью для связи с памятью и устройствами ввода-вывода, поэтому в память можно записать или считать единовременно только 8 бит. Регистр защелка адреса RG КР580ИР82. При обращении к памяти МП передает по ШАД адрес ячейки памяти, этот адрес записывается в регистр сигналом ALE, генерируемым МП в этот момент поступающем на вход регистра. Адрес хранится в регистре на время последующей передачи данных.

3. Программируемый таймер К1810ВИ54 предназначен для генерации времязадающих функций, программно-управляемых временных задержек с возможностью программного контроля их выполнения. В данном устройстве таймер необходим для формирования сигналов запуска контроллера ПДП. Таймер как и МП тактируется от генератора КР1810ГФ84 импульсами PCLK которые вдвое меньше частоты CLK.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.