1 Анализ и концепция реализации

Устройство должно обеспечить удобство ввода информации в требуемом шестнадцатеричном формате, при этом желательно, чтобы оно было как можно проще и содержало минимум элементов.

Согласно дополнительным сведениям необходимо использовать 16-ти разрядный процессор 8086. Это требование в преимущественно определяет архитектуру аппаратной части устройства.

Так как процессор 16-ти разрядный, то соответственно шина данных будет 16 разрядов, это определяет требование – 16-ти разрядные ОЗУ и ПЗУ.

Требование накопления 1000 значений определяет объем ОЗУ необходимого для хранения такого числа байт информации. То есть необходимо иметь ОЗУ объемом не менее 1024 байт – 1 кБ.

Количество разрядов индикации влияет на выбор способа индикации и конкретного индикатора.

Вид способа ввода и формата вводимых данных определяет размер клавиатуры, так как это 16-тиричные цифры, то необходимо иметь клавиатуру из 16 цифирных кнопок и нескольких дополнительных – функциональных. Помимо этого требуется обеспечить подавление дребезга к клавиатуре.

1.2 Построение аппаратной части устройства

Проанализировав эти требования техническая реализация аппаратной части устройства будет следующей:

Для тактирования процессора будет использоваться штатный генератор и формирователь сигналов сброса и ожидания 1018ГФ84.

Адресация устройств будет совмещенной, так как памяти достаточно и ее экономия в данном случае не требуется.

Для дешифрации адреса будет использоваться внешний дешифратор, который позволит абсолютно исключить конфликты адресов.

Для демультиплексирования 16-ти разрядного адреса воспользуемся два 8-ми разрядными статическими регистрами с защелкой по срезу.

Аналогичным образом поступим с шинными формирователями.

В качестве ПЗУ воспользуемся микросхемами с УФ стиранием содержимого, как наиболее доступными и недорогими. В схеме их будет две, так как разрядность каждой 8, а необходимо 16. Включение будет совместным (с соединенными адресными линиями).

Для ОЗУ также применим две 8-ми разрядные микросхемы. В качестве типа памяти используем статическую, так как объема достаточно и не требуется дополнительных контроллеров, которые сильно усложняют устройство.

Для индикации и ввода данных с клавиатуры удобнее всего воспользоваться существующим контроллером клавиатуры и дисплея 8089. Его применение сразу решает проблему подавления дребезга. Контроллер обеспечивает динамический тип индикации, что экономит количество навесных элементов и сложность их монтажа. В качестве индикатора воспользуемся 7-ми сегментным светодиодным с общим анодом. Дешифрацию кодов будем осуществлять программно – это проще и сокращает число элементов в схеме.

Для оперативной обработки событий в контроллере клавиатуры и дисплея его выход запроса прерывания соединим с входом немаскируемых прерываний процессора.

По этим соображениям построена функциональная схема, по которой уже разрабатывалась принципиальная.

1.3 Описание принципиальной схемы

На микросхеме DD4 реализован генератор тактовой частоты для процессора, также формирователь сигнала сброса и ожидания. Эти сигналы подаются на соответствующие входы процессора. Сигнал тактирования снимается с выхода CLK, это соответствует тому, что он образован делением собственной частоты первой гармоники кварцевого резонатора на 3.

Микросхема DD6 это сам процессор, который включен по типовой схеме. Процессор работает в минимальном режиме, для этого вход выбора режима работы NM/MX соединен с шиной питания посредством резистора. Для умощнения выводов сигналов чтения и записи эти сигналы поданы на повторители выполненные на логических элементах И микросхемы DD5. Это необходимо для того чтобы обеспечить нормальный электрический режим выходных цепей, так как они рассчитаны на подключения только одного входа ТТЛ.

Для «защелки» - демультиплексирования адреса и сохранения мультиплексированного сигнала BHE – Byte Hight Enable применены регистры DD8 и DD9. Так как их выключение не требуется, то их входы активизации выходов подключены к общей шине. Управление защелкой (стробирование) осуществляется непосредственно с процессора сигналом ALE (STROB) – Adres Load Enable.

Для работы с шиной, нагруженной на большое число входов-выходов предназначены шинные формирователи DD10 и DD11. Активацией (переход в активный режим из 3-го высокоимпедансного состояния) их выходов управляет процессор посредством сигнала DEN – Data Enable. Для управления направлением передачи используется сигнал Т – Trace.

С выходов регистров адреса адрес и сигнал выбора старшего байта поступает на адресные входы ПЗУ и ОЗУ. Сигнал BHE на вход выбора кристалла микросхемы старшего банка ОЗУ. Помимо этого три старших разряда поданы на входы дешифратора адреса DD7 – это обеспечивает выбор устройств по старшей 16-тиричной цифре в адресе в 16-тиричном формате.

Дешифратор DD7 преобразует код с разрядов А14, А13, А12 шины адреса в позиционный код. Таким образом, так как выходы дешифратора соединены с конкретными устройствами, то в любой момент времени активно может быть только одно устройство. Для ПЗУ посредством схемы логического И объединены два выхода дешифратора, что соответствует наличию у него двух адресов. Дешифратор активируется только в моменты обращения (чтения или записи) к любому из устройств, для этого сигналы чтения и записи объединены схемой логического И и ее выход подан на вход выбора кристалла дешифратора.

ОЗУ DD14 и DD15, а также ПЗУ DD12 и DD13 адресными входами подключены к адресной шине, информационными выходами к шине данных. Схема включения типовая и особенностей не имеет. ПЗУ своим младшим битом подключены ко второму биту шины адреса, и так далее, т е первый не используется, это возможно потому, что процессор считывает данные из ПЗУ не побайтно, а словами. В ОЗУ же чтение осуществляется как побайтно, так и словами, для этого и служит сигнал BHE. Вход управления записью/чтением ОЗУ подключен к выходу сигнала записи (WR) процессора. Когда идет чтение там лог.1 – активен режим чтения ОЗУ, когда запись там лог.0 – активен режим записи в ОЗУ.

Функцию индикации и опроса клавиатуры выполнят специализированный контроллер клавиатуры и дисплея DD1. Его схема включения в микропроцессорную систему стандартная и особенностей не имеет. Шина данных у него 8-ми разрядная и подключена к младшим 8-ми разрядам шины данных. Сигналы WR и RD подключены к соответствующим выходным сигналам процессора. Выход сигнала запроса прерывания подключен к входу запроса немаскируемого прерывания процессора. Выбор кристалла осуществляется посредством соединения входа CS с одним выходом дешифратора DD7. Вход, определяющий к чему идет обращение (к регистру данных или к регистру управления/состояния), соединен с младшим разрядом адресной шины – это соответствует наличию у этого контроллера двух адресов.

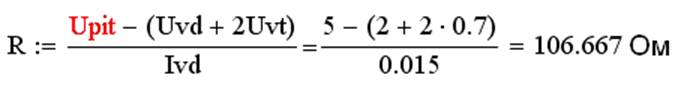

Для умощнения выходов контроллера применен внешний шинный формирователь DD2 который в таком включении будет транслировать сигналы с входа на выход. Выход в свою очередь подключен к выводам сегментов индикатора через токоограничивающие резисторы. Сопротивление резисторов определяется по формуле:

где: Upit – напряжение питания, В

Uvd – падение напряжения на светодиоде, В

Uvt – падение напряжения на выходном транзисторе микросхемы, В

Ivd – ток через светодиод, А.

Получив значение 106,7 Ома, берем ближайшее из ряда сопротивлений Е12 то есть это 110 Ом.

Для управления разрядами индикатора и сканирования столбцов клавиатуры применен дешифратор DD3. Таким образом, контроллер будет работать в режиме с внешней дешифрацией. Линии строк клавиатуры соединены с входами возврата – типовая схема.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.