when "0111" => outdc_2 <= "0000000010000000";

when "1000" => outdc_2 <= "0000000100000000";

when "1001" => outdc_2 <= "0000001000000000";

when "1010" => outdc_2 <= "0000010000000000";

when "1011" => outdc_2 <= "0000100000000000";

when "1100" => outdc_2 <= "0001000000000000";

when "1101" => outdc_2 <= "0010000000000000";

when "1110" => outdc_2 <= "0100000000000000";

when "1111" => outdc_2 <= "1000000000000000";

when others => outdc_2 <= "0000000000000000";

end case;

end if;

end process;

process (DC_1_ENABLE, outcounter_3)

begin

if DC_1_ENABLE = '0' then

outdc_3 <= "0000000000000000";

else

case outcounter_3 is

when "0000" => outdc_3 <= "0000000000000001";

when "0001" => outdc_3 <= "0000000000000010";

when "0010" => outdc_3 <= "0000000000000100";

when "0011" => outdc_3 <= "0000000000001000";

when "0100" => outdc_3 <= "0000000000010000";

when "0101" => outdc_3 <= "0000000000100000";

when "0110" => outdc_3 <= "0000000001000000";

when "0111" => outdc_3 <= "0000000010000000";

when "1000" => outdc_3 <= "0000000100000000";

when "1001" => outdc_3 <= "0000001000000000";

when "1010" => outdc_3 <= "0000010000000000";

when "1011" => outdc_3 <= "0000100000000000";

when "1100" => outdc_3 <= "0001000000000000";

when "1101" => outdc_3 <= "0010000000000000";

when "1110" => outdc_3 <= "0100000000000000";

when "1111" => outdc_3 <= "1000000000000000";

when others => outdc_3 <= "0000000000000000";

end case;

end if;

end process;

process (DC_1_ENABLE, outcounter_4)

begin

if DC_1_ENABLE = '0' then

outdc_4 <= "0000000000000000";

else

case outcounter_4 is

when "0000" => outdc_4 <= "0000000000000001";

when "0001" => outdc_4 <= "0000000000000010";

when "0010" => outdc_4 <= "0000000000000100";

when "0011" => outdc_4 <= "0000000000001000";

when "0100" => outdc_4 <= "0000000000010000";

when "0101" => outdc_4 <= "0000000000100000";

when "0110" => outdc_4 <= "0000000001000000";

when "0111" => outdc_4 <= "0000000010000000";

when "1000" => outdc_4 <= "0000000100000000";

when "1001" => outdc_4 <= "0000001000000000";

when "1010" => outdc_4 <= "0000010000000000";

when "1011" => outdc_4 <= "0000100000000000";

when "1100" => outdc_4 <= "0001000000000000";

when "1101" => outdc_4 <= "0010000000000000";

when "1110" => outdc_4 <= "0100000000000000";

when "1111" => outdc_4 <= "1000000000000000";

when others => outdc_4 <= "0000000000000000";

end case;

end if;

end process;

process (outdc_1, outdc_2, outdc_3, outdc_4)

begin

outor_1(0) <= outdc_1(5) or outdc_1(6) or outdc_1(7);

outor_1(1) <= outdc_2(5) or outdc_2(6) or outdc_2(7);

outor_1(2) <= outdc_3(5) or outdc_3(6) or outdc_3(7);

outor_1(3) <= outdc_4(5) or outdc_4(6) or outdc_4(7);

end process;

process (outor_1, S_0, S_1, DC_1_ENABLE)

begin

if (DC_1_ENABLE='1') then

outmux <= '0';

end if;

if (S_0 = '1') then

if (S_1 = '1') then

outmux <= outor_1(3);

else

outmux <= outor_1(2);

end if;

else

if (S_1 = '1') then

outmux <= outor_1(1);

else

outmux <= outor_1(0);

end if;

end if;

end process;

process (CLK_2, RESET_2, outmux)

variable COUNT : std_logic_vector (3 downto 0);

begin

if RESET_2 = '1' then

COUNT := "0000";

elsif CLK_2'EVENT and CLK_2 = '1' and outmux = '1' then

COUNT := COUNT + "0001";

end if;

outcounter <= COUNT;

end process;

process (DC_2_ENABLE, outcounter)

begin

if DC_2_ENABLE = '0' then

outdc <= "0000000000000000";

else

case outcounter is

when "0000" => outdc <= "0000000000000001";

when "0001" => outdc <= "0000000000000010";

when "0010" => outdc <= "0000000000000100";

when "0011" => outdc <= "0000000000001000";

when "0100" => outdc <= "0000000000010000";

when "0101" => outdc <= "0000000000100000";

when "0110" => outdc <= "0000000001000000";

when "0111" => outdc <= "0000000010000000";

when "1000" => outdc <= "0000000100000000";

when "1001" => outdc <= "0000001000000000";

when "1010" => outdc <= "0000010000000000";

when "1011" => outdc <= "0000100000000000";

when "1100" => outdc <= "0001000000000000";

when "1101" => outdc <= "0010000000000000";

when "1110" => outdc <= "0100000000000000";

when "1111" => outdc <= "1000000000000000";

when others => outdc <= "0000000000000000";

end case;

end if;

end process;

process (outdc)

begin

outor <= outdc(3) or outdc(4);

end process;

outxnor_1 <= outxnor(0);

outxnor_2 <= outxnor(1);

outxnor_3 <= outxnor(2);

outxnor_4 <= outxnor(3);

outcounter_11 <= outcounter_1;

outcounter_12 <= outcounter_2;

outcounter_13 <= outcounter_3;

outcounter_14 <= outcounter_4;

outdc_11 <= outdc_1;

outdc_12 <= outdc_2;

outdc_13 <= outdc_3;

outdc_14 <= outdc_4;

outor_11 <= outor_1;

outmux_11 <= outmux;

outcounter_21 <= outcounter;

outdc_21 <= outdc;

TARGET <= outor;

end Behavioral;

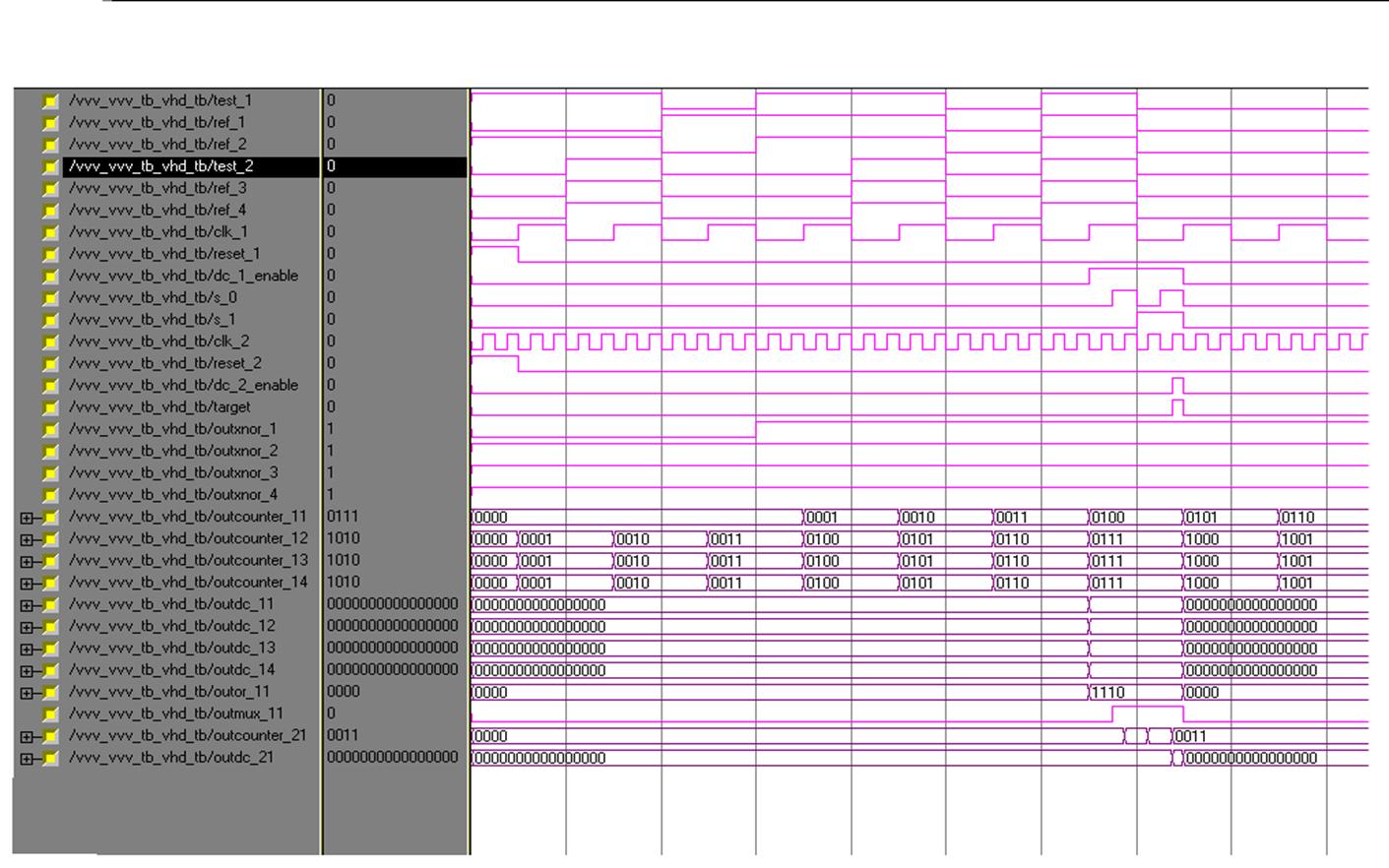

Рисунок 1. Диаграмма работы решающего устройства

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.