Центральные устройства ЭВМ

Основная память

Структура памяти ЭВМ, ее состав и принцип действия

Для совр. ЭВМ характерна модульность и децентрализация управления. Вследствие этого является магистральность, т.е. шинный принцип организации структуры на основе иерархии построения и управления ЭВМ, обеспечивающие согласованные, т.е. скоординированные устройства ЭВМ и выполнение требуемых операций снизу вверх при управлении сверху.

Иерархический принцип построения и управления характерен не только для ЭВМ в целом, но и для отдельных ее подсистем, в частности для памяти, это объясняется тем, что для пользователей желательно иметь ЭВМ с ОЗУ большой емкости и высоким быстродействием, однако одноуровневое построение памяти не позволяет одновременно удовлетворять этим параметрам, поэтому память совр. ЭВМ строится по многоуровневому пирамидальному принципу. Ядро процессора (ЦП) ЭВМ образует процессор и процессорную память, состоящую из ОЗУ и ПЗУ.

Для повышения быстродействия в состав ЦП может входить СОЗУ (сверхоперативное ЗУ) с небольшой емкостью и образованная из нескольких десятков регистров с быстрым временем доступа.

В СОЗУ хранятся данные, используемые в обработке. Время считывания в 10-20 раз меньше, чем в ОЗУ. По назначению используемые регистры делятся на регистры хранения и регистры сдвига.

Регистры может быть объединены в единую структуру, возможности которых зависят от способа доступа и адресации регистров. Если к любому регистру можно обратиться для записи или чтения по его адрему, то такая регистровая память называется СОЗУ с произвольным доступом.

Безадресные регистровые структуры могут образовывать 2 вида устройств памяти:

1. память магазинного типа

2. память с выборкой по содержанию (ассоциативная)

Память магазинного типа

образуется из последовательно соединенных регистров. Запись данных в

регистровую структуру можно осуществлять через один регистр. Такая память

является аналогом линии задержки (FIFO)

Память магазинного типа

образуется из последовательно соединенных регистров. Запись данных в

регистровую структуру можно осуществлять через один регистр. Такая память

является аналогом линии задержки (FIFO)

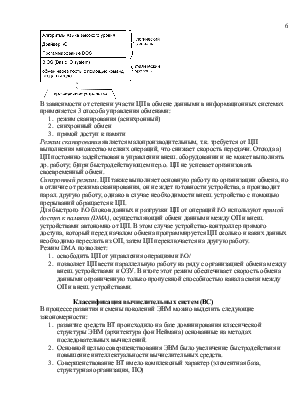

При записи слова в стековую память, содержимое смещается в сторону последнего регистра

Если стек полностью заполнен, то число из последнего регистра теряется. Затем записывается число в вершину стека (RG1), считывается с RG1. После того, как число считано, содержимое стека смещается в сторону RG1.

Стековая память получила широкое распространение. Она может быть реализована как с помощью специальных м\м, так и эмулировать в ОЗУ программным способом, для этого в основной памяти выделяется некоторая ее часть. Специальный регистр МП – указатель стека – постоянно хранит адрес ячейки основной памяти, выполняющей функции вершины стека. Чтение чисел производится из вершины стека, после чего указатель стека изменяется и указывает следующую ячейку стековой памяти. При записи – замена прежнего номера ячейки указателя стека на номер очередной свободной ячейки, после чего производится запись числа по этому адресу. Такая работа указателя стека позволяет реализовывать метод «первый вошел- последний вышел» (FILO)

В стек может быть загружен в определенной очередности ряд данных, которые считываются из стека в обратном порядке. На этом свойстве построена система ариф. преобразований, называемой логикой Лукашевича.

В безадресной памяти с выборкой по содержанию обращение происходит с помощью специальной маски, которая содержит поисковый образ. Информация считывается из памяти в том случае, если определенная ее часть соответствует поисковому образу, зафиксированному в маске. В МП ассоциативные ЗУ используют в составе КЭШ-памяти (память блокнотного типа).

КЭШ-память- буферное ЗУ, предназначенное для хранения активных страниц (10-100кб) кэш-память как более быстродействующая благодаря ассоциативной выборки данных, предназначена для ускорения выборки команд программы и обрабатываемых данных. При этом нет необходимости обращаться к ОЗУ за следующей командой или операндом. Достаточно поместить в маску необходимый адрес и если искомая информация имеется в СОЗУ, то она сразу будет выбрана.

Обращение к ОЗУ будет необходима только лишь при отсутствии требуемой информации в СОЗУ. Благодаря такому использованию СОЗУ сокращается число обращений к ОЗУ ЭВМ, следовательно повышается ее быстродействие.

Кэш-память может быть размещена в кристалле МП (кэш-память 1ого уровня), либо выполнена в виде отдельной м\мы (внешняя кэш-память или кэш-память 2ого уровня)

1 уровень кэш-памяти P133 – 16 кб, время доступа – 5-10нс (обработка 32-битного слова), пропускная способность до 667 Мб\с.

Внешняя кэш-память до 1 Мб, время доступа ~15нс, 64 битное слова, пропускная способность 528 Мб\с.

Кэш-память предназначена для ускорения выборки команд и данных, сами программы пользователей и данные к ним размещаются в ОЗУ. Кроме того, часть машинных программ, обеспечивающих автоматическое управление вычислениями и используемых наиболее часто, могут размещаться в ПЗУ основной памяти.

На более низких уровнях иерархии используют внешние ЗУ на магнитных носителях (более низкое быстродействие, оч. большая емкость) Организация обмена информационными потоками ЗУ разных уровней при децентрализованному управлении этими устройствами позволяют рассматривать иерархическую структуру памяти как единую абстрактную виртуальную память. Согласованная работа ЗУ всех уровней обеспечивается под управлением программ ОС, при этом пользователь получает возможность работать с памятью намного превышающей емкость ОЗУ.

Центральный процессор (ЦП) ЭВМ.

Структура базового МП.

Основа ПК – ЦП – устройство для выполнения ариф. и лог. преобразований данных, для обращения к ОЗУ и внешним ЗУ, для управления кодом вычислительных процессов.

В настоящее время большое число различных МП, различных по назначению, функциональным возможностям, структуре и исполнению. Наиболее существенным классификационным признаком всех МП является количество разрядов в обрабатываемом блоке информации. (8,16,32-битные МП). Начиная с МП 80846 в кристалле МП размещается арифм. сопроцессор для выполнения операций с плавающей запятой.

Intel разработала специальный МП overdrive, предназначенный для параллельной работы с основным МП. Усовершенствования, внесенные Intel в МП сделали ПК серии IBM PC мультипрограммными, многопользовательскими, многозадачными.

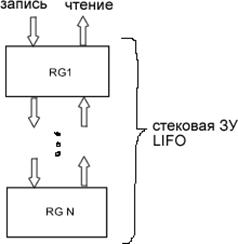

Структура МП Intel:

К управляющим регистрам МП относится регистр флага, каждый разряд которого имеет строго определенное назначение. Все флаги младшего байта регистра устанавливаются ариф. или лог. операциями.

Флаги старших байтов за исключением флага переполнения устанавливаются программным путем.

Взаимодействие элементов при работе МП.

Работой МП управляет программа в ОЗУ, адрес очередной команды хранится в счетчике команд IP и в одном из сегментных регистров, чаще всего в CS. Каждый из них в реальном режиме – длина 16 бит, физический адрес в основной памяти должен иметь длину 20 бит. Это несогласованность приводит к тому, что в командах невозможно указать физический адрес основной памяти, его приходится собирать из разных регистров МП в ходе его работы. В реальном режиме вся основная память делится на сегменты по 64 кб, адрес основной памяти разделен на 2 части: № сегмента в ОП (базовый сегмент) и № ячейки внутри сегмента (смещение относительно начала сегмента). Базовый адрес образуется путем добавления № сегмента четырех нулей, поскольку последние 4 разряда абсолютного адреса всегда нулевые, сегмент может начинаться не с любой ячейки, а только с «параграфа», т.е. с начала 16 байтного блока.

В структуре МП имеется несколько сегментов, № ячейки внутри сегмента называется исполнительным адресом.

В большинстве случаев в адресной части команды указывается именно исполнительный адрес (№ сегмента подразумевается по умолчанию). Иногда указывается полный адрес в виде префексной структуры (сегмент-смещение). Если сегмент в команде не указывается, значит работа ведется внутри текущего сегмента. № сегмента, как и смещение имеет 2 байта. При вычислении физ. адреса основной памяти сегменты и смещения суммируются, но сегмент перед суммированием смещается влево на 4 бита, т.о. образуется физ. адрес в 20 бит.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.