Режим 4 (программная задержка строба). После записи CW на выходе OUT устанавливается 1. Запуск счета осуществляется после загрузки DW. При достижении 0 на выходе OUT генерируется импульс длительностью в один период CLK. а CE продолжает работать. Перезагрузка CE во время счета приводит к перезапуску CE. Генерация 0 на входе GATE приостанавливает счет.

Режим 5 (аппаратная задержка строба). Счетчик начинает работать только по фронту GATE. Новый фронт перезапускает текущий счет. В остальном режим подобен предыдущему.

Во всех режимах сигнал GATE является управляющим: запрещает счет низким уровнем напряжения и (или) перезапускает фронтом.

9. Программирование PIT К1810ВИ54.

Программирование сводится к загрузке в него управляющего слова и константы пересчета.

Формат управляющего слова:

Защелкивание – значение CE записывается в OL. Последующими командами чтения можно считать значение OL.

Код 2/10 – двоичный (от 0 до F) или десятичный (от 0 до 9) счет.

Пусть необходимо запустить первый канал таймера в режим 0 с десятичным счетом и загрузить константу 9998. Базовый адрес таймера E0.

MVI A, 01110001 b ; в аккумулятор заносим управляющее слово

OUT E3h ; выдаем управляющее слово в ПИТ: БазАдр+3

MVI A,98h ; в аккумулятор – младший байт

OUT E1h ; младший байт константы – в первый канал БазАдр+1

MVI A,99h ; в аккумулятор – старший байт

OUT E1h ; старший байт константы – в первый канал БазАдр+1

Сразу после выполнения последней команды, если на линии GATE первого канала 1, то канал таймера 1 начнет работу в режиме 0.

10. Форматы команд и слова состояния PIT К1810ВИ54

В режимах 0, 2, 3 и 4 при GATE=0 можно выполнить команду чтения каналов таймера. После первой команды IN будет считана младшая половина счетчика, после второй – старшая.

Для корректного считывания канала таймера необходимо выполнить команду CLC, когда посылается в регистр управляющего слова следующий байт:

После посылки управляющего слова следующими двумя командами IN из указанного канала можно считать сначала младший а затем старший байт текущего значения счетчика таймера. Считывание выполняется не ранее чем через 2 такта синхронизации.

Для считывания регистра состояния канала таймера используется команда RBC, когда посылается в регистр управляющего слова следующий байт:

Пусть базовый адрес таймера 78h и надо защелкнуть слово состояния и счетчик каналов для канала 0.

MVI A,11000010b ; Посылка RBC по БазАдр+3

OUT 7Bh ;

IN 78h ; Считываем слово состояния канала 0 по БазАдр+0

MOV D,A ; Сохраняем в регистре D

IN 78h ; Считываем младший байт счетчика канала 0 по БазАдр+0

MOV C,A ; Сохраняем в регистре C

IN 78h ; Считываем старший байт счетчика канала 0 по БазАдр+0

Слово состояния канала таймера:

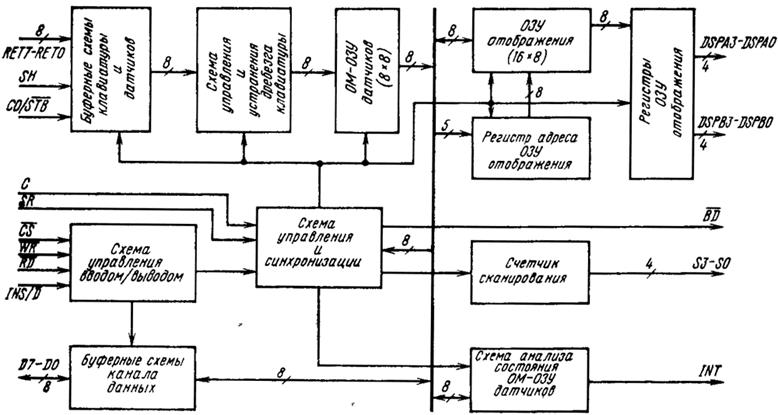

11. Структура и внешние выводы БИС К580ВД79.

Этот контроллер освобождает процессор от операции сканирования клавиатуры и регенерации изображения на индикаторных матрицах.

Устройство управления вырабатывает сигналы управления обменом данными между МП и внутренними регистрами, буферными схемами ПККД. На входе синхронизации CLK тактовая частота должна быть не менее 200кГц для устойчивой работы схем регенерации. Линия A0 – вход внутренней адресации, Если A0=1, адресуются команды и слова состояния, если A0=0 – адресуются данные.

Сигналы CS, WR, RD служат для активизации, записи и чтения соответственно.

Сигнал RESET (длительность не мене 6 тактов CLK) приводит микросхему ПККД в начальное состояние, не изменяя состояния ОЗУ. Устройство управления реализует функцию внутренней синхронизации и вырабатывает сигнал BD для гашения изображения на дисплее. Длительность этого сигнала должна быть не менее 150мкс.

12. Режимы работы блока управления клавиатурой БИС К580ВД79.

Блок управления клавиатурой обеспечивает ввод через буферные регистры в ОЗУ клавиатуры информации о состоянии линий возврата RL0-RL7 Кроме того обеспечивается устранение дребезгов и определение одновременного нажатия нескольких клавиш.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.