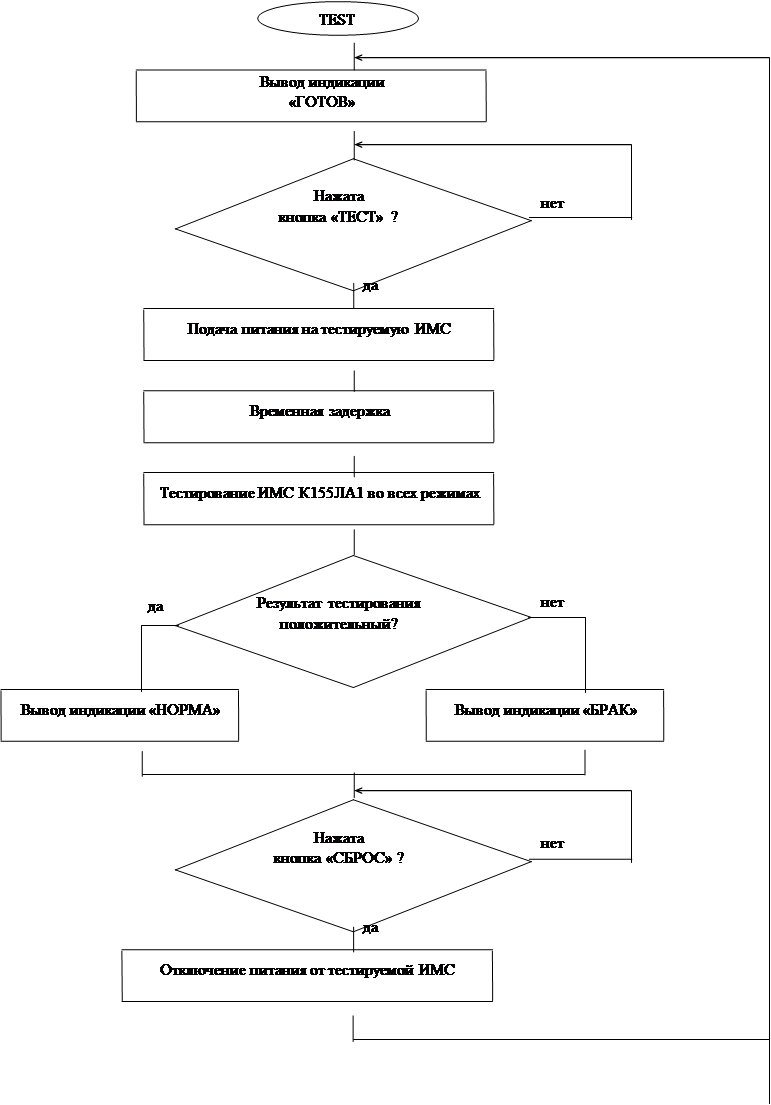

3. Обобщенная блок-схема алгоритма работы тестера

Обобщенная блок-схема алгоритма работы тестера разрабатывается исходя из требований, предъявляемых к тестеру.

· После включения электропитания (подачи сигнала начальной установки на вход SRОЭВМ) загорается индикатор «ГОТОВ».

· После выдачи сигнала «ГОТОВ» микроЭВМ переходит в режим ожидания нажатия кнопки «ТЕСТ». Кнопка «ТЕСТ» нажимается оператором после установки в сокет тестируемой ИМС. Затем микроЭВМ коммутирует питание тестируемой ИМС и производит ее полную функциональную проверку во всех возможных режимах.

· В случае успешного теста ИМС во всех режимах загорается индикатор «НОРМА», а если хотя бы в одном из проверяемых режимов зафиксирован неверный выходной логический уровень, загорается индикатор «БРАК».

· Информация о результате тестирования выводится до тех пор, пока оператор не нажмет кнопку «СБРОС». После нажатия кнопки «СБРОС» от тестируемой ИМС отключается электропитание и проверенную микросхему можно извлечь из сокета. Программа тестирования после этого должна создать исходные условия для тестирования следующего корпуса ИМС: вывести сигнализацию «ГОТОВ» и т.д.

|

|

|

|

|

||||||

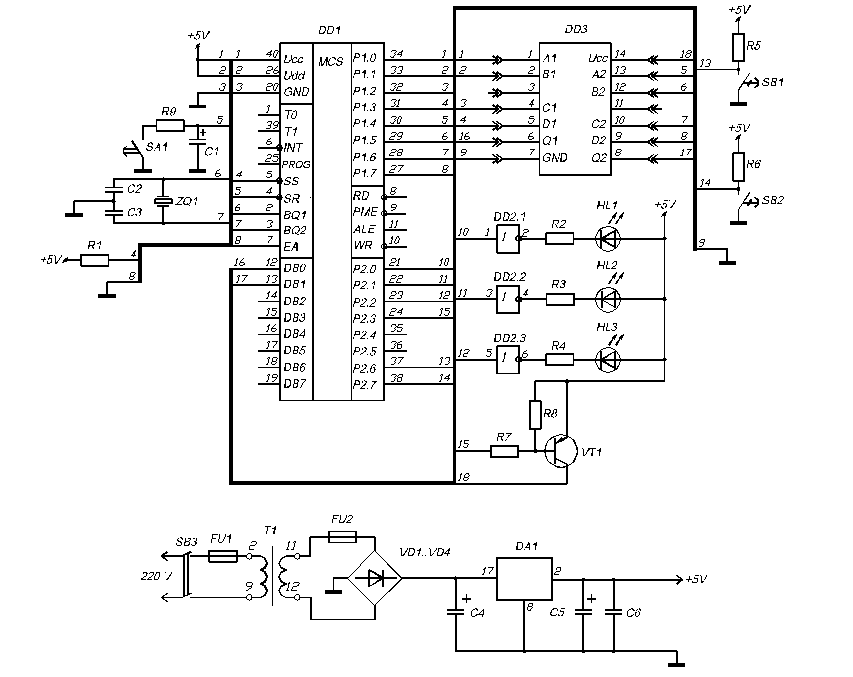

Рис. 3. Тестер ИМС К155ЛА1. Схема электрическая принципиальная

Схема электрическая принципиальная тестера ИМС К155ЛА1 приведена на рис. 3. Она выполнена на основе ОЭВМ КМ1816ВЕ48 (DD1), включенной в автоматическом режиме (SS = «1») с внутренней памятью команд (EA = «0»), без использования тестовых входов T0, T1 и входа прерывания INT.

Так как вход ОЭВМ SR внутри корпуса ОЭВМ через резистор 200 кОм соединен с источником питания +5 В, для обеспечения системного сброса ОЭВМ при подаче питания достаточно к входу SRподключить внешний конденсатор С1 (1 мкФ). Кнопка SA1 с разрядным резистором R9 служит для оперативной начальной установки тестера.

Для обеспечения генерации тактовой частоты ОЭВМ, к входам BQ1 и BQ2 подключен кварцевый резонатор ZQ1(5 МГц) и конденсаторы C2 и С3 (30 пФ). Выводы Ucc и Udd присоединены к источнику питания +5В, а вывод GND – к общей точке прибора.

Входы тестируемой ИМС (A1, B1, C1, D1, A2, B2, C2, D2) подключены к выводам порта P1 ОЭВМ, а выходы тестируемой ИМС (Q1 и Q2) подключены к выводам DB0 и DB1 порта BUS. Электронный ключ, осуществляющий подачу напряжения питания на тестируемую ИМС, управляется от линии P2.3 ОЭВМ. Линии порта P2 используются для индикации режима работы тестера (P2.0 – «ГОТОВ», P2.1 – «НОРМА», P2.2 – «БРАК») и подключения управляющих кнопок «СБРОС» (P2.6) и «ТЕСТ» (P2.7). Кнопки SB1 и SB2 имеют общую планку фиксации, т.е. в нажатом состоянии может быть лишь одна из них. Резисторы R5 и R6 служат для ограничения тока, потребляемого от источника питания +5 В при замыкании кнопок соответственно SB1 и SB2. Номинал этих резисторов выбирается равным 4.7 КОм.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.