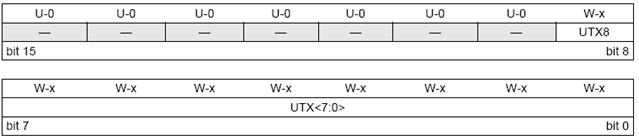

UxTXREG: Регистр передатчика (Только для записи)

бит 15-9Неосуществленный: Читается как ‘0’

бит 8UTX8: Информационный 8-й разряд в передающимся символе (в 9-ти битном режиме работы)

бит 7-0UTX <7:0>: Информационные разряды 7-0 в передающимся символе

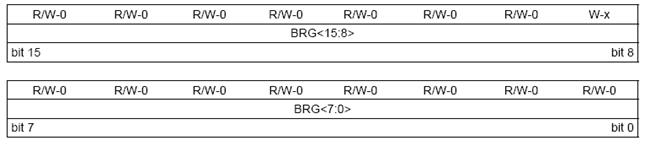

UxBRG: UARTx Регистр скорости

бит 15-0BRG <15:0>: биты Делителя Скорости Baud Rate

3. ГЕНЕРАТОР СКОРОСТИ (Baud Rate) модуля UART

Модуль UART включает специальный 16-разрядный Генератор Baud Rate (BRG). Регистр UxBRG управляет периодом, 16-разрядного таймера.

![]() Формула

1

Формула

1

![]() Формула 2

Формула 2

где:FCY обозначает частоту циклов команды (FOSC/2).

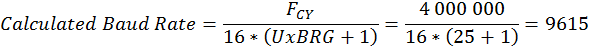

Пример1 показывает вычисление ошибки Baud Rate для следующих условий:

FCY=4MHz

Desired Baud Rate = 9600 - желательная скорость

По формуле 1 находим

![]()

Округляем значение до ближайшего целого

![]()

Тогда реальную скорость можно рассчитать по формуле 1

Тогда ошибка рассчитывается следующим образом

![]()

Максимально возможная Baud Rate (BRGH = 0) – это FCY/16 (для UxBRG = 0), и минимально возможная Baud Rate - это FCY / (16 * 65536).

Формулы 3, 4 показывают как вычислить Baud Rate с BRGH = 1

![]() Формула

3

Формула

3

![]() Формула 4

Формула 4

Максимальная возможная Baud Rate (BRGH = 1) - это FCY/4 (для UxBRG = 0), и минимально возможная Baud Rate - это FCY / (4 * 65536).

При записи нового значения в регистр UxBRG заставляет таймер BRG сброситься. Это гарантирует, что BRG не будет дожидаться своего переполнения для того чтобы перейти на новую скорость.

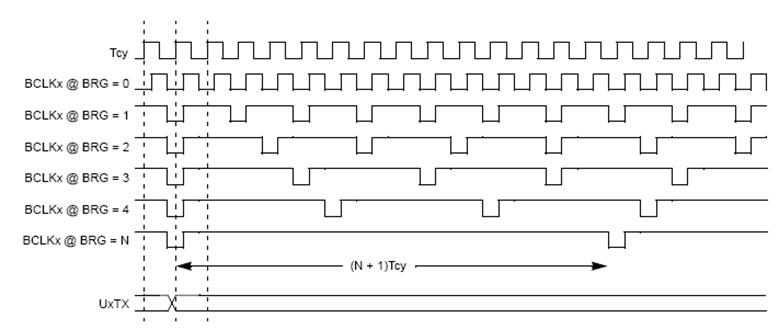

3.1. BCLKx Вывод

Вывод BCLKx может быть выходом 16-ти кратных битовых тактов, если UART и вывод BCLKx включены

(UEN <1:0> = 11). Эта особенность используется для внешней поддержки кодера/декодера IrDA (смотреть рисунок 2). Вывод BCLKx остается в высоком состоянии в течение режима Sleep. BCLKx настроен как выход пока UART находится в этом режиме (UEN <1:0> = 11), независимо от состояния битов TRISx и PORTx.

Рисунок 2. BCLKx Output vs. UxBRG Programming

4. Настройка модуля UART

UART использует стандартный формат (NRZ) без возвращения к нулю (один START бит, восемь или девять битов данных, и один или два Стоповых бита). Четность поддерживается аппаратными средствами и может быть конфигурирована пользователем следующим образом: четный, нечетный, или без четности. Самый обычный формат данных - 8 битов, без четности, и один Стоповый бит (обозначается как 8, N, 1), который является значением по умолчанию после сброса POR. Количество информационных битов, количество стоповых битов и чётность определены в битах PDSEL <1:0> (UxMODE <2:1>) и STSEL (UxMODE <0>). В микроконтроллере имеется специальный 16 разрядный генератор Baud Rate который может использоваться, чтобы получить стандартного Baud Rate от генератора. UART передает и получает младший бит (LSb) первым. Передатчик модуля UART и приёмник функционально независимы, но они используют тот же самый формат данных и Baud Rate.

4.1 Включение UART

Модуль UART включается установкой бита UARTEN (UxMODE <15>) и бита UTXEN (UxSTA <10>). После включения, выводы UxTX и UxRX конфигурируются как выход и вход соответственно, отменяя настройку регистров TRIS и PORT для соответствующего входа/выхода {I/O}. Вывод UxTX имеет логическую ‘1’, когда не происходит передача.

Обратите внимание: бит UTXEN не должен быть установлен, пока UARTEN бит не будет установлен, иначе передача UART не будет производиться.

4.2. Отключение UART

Модуль UART отключается путём сброса бита UARTEN (UxMODE <15>). Это состояние является по умолчанию после любого сброса. Если UART отключён, тогда все выводы UART работают как выводы порта под управлением их соответствующих битов PORT и TRIS.

Отключение модуля UART очищает буферы. Любые символы данных в буферах теряются и счетчик Baud Rate сбрасывается.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.