11 = 9-ти битные данные, без чётности

10 = 8-ми битные данные, проверка на нечётность

01 = 8-ми битные данные, проверка на чётность

00 = 8-ми битные данные, без чётности бит 0STSEL: Выбор количества стоповых битов

1 = 2 Стоповых бита

0 = 1 Стоповый бит

Примечание 1:Эта особенность доступна только для режима Low-Speed (BRGH =0).

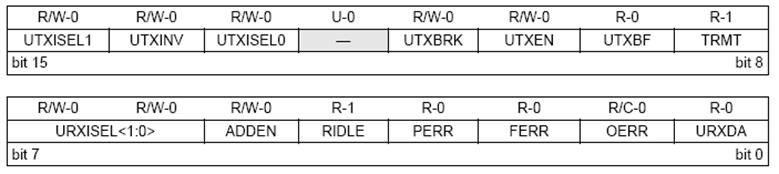

UxSTA: Регистрстатусаиуправления UARTx (Status and Control Register)

бит 15,13UTXISEL <1:0> биты Выбора Режима Прерывания при Передачи

11 = зарезервированный

10 = генерируется прерывание, когда символ перемещён в передающий сдвиговый регистр и передающий буфер становится пустым

01 = генерируется прерывание, когда передан последний символ (то есть, последний символ был перемещён из передающего сдвигового регистра) и все передающие операции закончены

00 = генерируется прерывание, когда любой символ перемещён передающему сдвиговому регистру (который подразумевает не менее одно пустого регистра в передающем буфере)

бит 14UTXINV: бит инверсии полярности передатчика

1 = UxTX в Idle - ‘1’

0 = UxTX в Idle - ‘0’

бит 12 Неосуществленный: Читается как ‘0’

бит 11UTXBRK: Бит перерыва (Break) передачи

1 = UxTX вывод управляется низким уровнем независимо от состояния передатчика (Sync Break transmission – Стартовый бит сопровождаемый двенадцатью ‘0’ и Стоповым битом)

0 = Sync Break передача заблокирована или завершена бит 10UTXEN: бит разрешения передачи

1 = UARTx передача разрешена; UxTX вывод управляется модулем UARTx (если UARTEN = 1)

0 = UARTx передача запрещена; любая передача, ждущая обработки, отменяется и буфер очищается; вывод UxTX управляется регистром PORT

бит 9UTXBF: бит состояния заполнения передающего буфера (только для чтения)

1 = передающий буфер, полон

0 = передающий буфер не полон, и можно записать в буфер ещё не менее одного символа бит 8TRMT: бит указывающий на то пустой или нет передающий сдвиговый регистр (только для чтения)

1 = передающий сдвиговый регистр пуст, и передающий буфер пуст (то есть, последняя передача закончилась)

0 = Передающий сдвиговый регистр не пуст, передача происходит или поставлена в очередь в передающем буфере бит 7-6URXISEL <1:0>: биты Выбора Режима Прерывания при Приёме

11 = бит флага прерывания устанавливается, когда буфер приёмника полон (то есть, имеет 4 символа данных)

10 = бит флага прерывания устанавливается, когда буфер приёмника полон на 3/4 (то есть, имеет 3 символа данных)

0x = бит флага прерывания устанавливается когда получен символ бит 5ADDEN: бит определения символа адреса (бит 8 из полученных данных = 1)

1 = режим определения адреса включён. Если 9 битный режим не выбран, то этот служебный бит не имеет никакого эффекта.

0 = режим определения адреса заблокирован бит 4RIDLE: бит Простоя Получателя (только для чтения)

1 = получатель простаивает

0 = данные получаются бит 3PERR: бит Состояния Ошибки Четности (только для чтения)

1 = ошибка четности была обнаружена для текущего символа

0 = ошибка четности не была обнаружена бит 2FERR: бит Состояния Ошибки кадровой синхронизации (только для чтения)

1 = ошибка кадровой синхронизации была обнаружена для текущего символа

0 = ошибка кадровой синхронизации не была обнаружена бит 1OERR: бит состояния ошибки переполнения приёмного буфера (очистка/только для чтения)

1 = получающий буфер переполнился

0 = получающий буфер не переполнился. (Сброс предварительно установленного бита OERR сбросит получающий буфер и RSR к пустому состоянию)

бит 0URXDA: бит доступности данных получающего буфера (только для чтения)

1 = получающий буфер имеет данные; но ещё не менее одного символа сможет быть прочитано

0 = получающий буфер пуст.

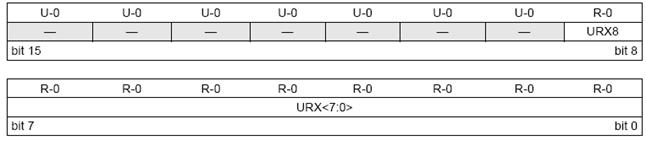

• UxRXREG: Регистр получателя (ReceiveRegister)

бит 15-9Неосуществленный: читается как ‘0’

бит 8URX8: Информационный разряд 8 из Полученного Символа (в 9-ти битном режиме работы)

бит 7-0URX <7:0>: Информационные разряды 7-0 из Полученного Символа

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.