- арифметические команды с переносом или заемом, типа ADC, SBB;

- команды сдвига с непосредственным операндом;

- команды с префиксами повторения и/или замены сегмента;

- некоторые FPU-команды (могут спариваться только с командой обмена FXCH) – FADD, FMUL, FDIV, FLD.

4. PV – команды этого класса могут выполняться в любом из конвейеров, но имеют возможность спариваться с другими командами только когда направляются в V-конвейер. К этому классу относятся:

- команды внутрисегментной передачи управления (JMP near, CALL near, Jcc);

- команда FXCH.

Условия спаривания (ParingRules)

Условием одновременного выполнения двух команд является их принадлежность к соответствующим классам: команда, которая направляется в U-конвейер, должна принадлежать классу UV или PU, а команда, которая направляется в V-конвейер – классу UV или PV.

Вторым важным условием спаривания команд является их взаимная независимость по данным. Спаривание двух соседних команд невозможно, если какой-либо регистр служит операндом-приемником для первой команды пары и операндом-источником для второй команды, или если обе команды используют один и тот же регистр в качестве операнда-приемника. Использование одного и того же регистра в качестве операнда-источника для двух соседних команд или в качестве источника для первой команды и приемника для второй не препятствует спариванию этих команд.

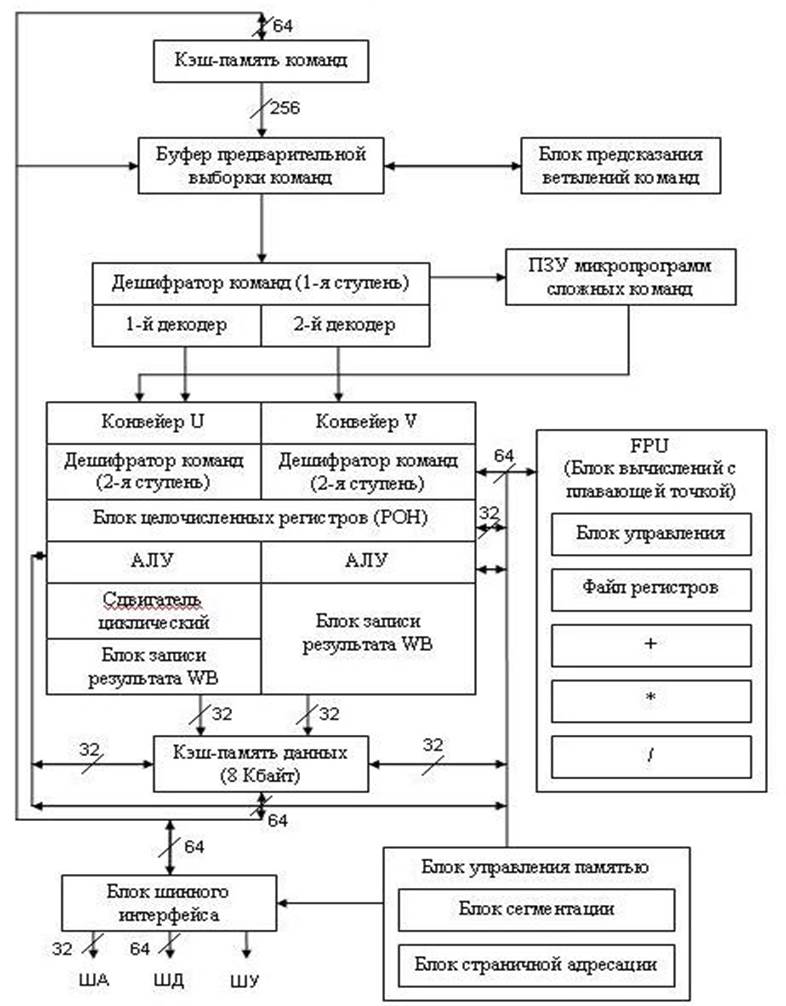

Упрощенная схема процессора

Из учебника В.Ф. Мелехина и Е.Г. Павловского «Вычислительные машины, системы и сети»:

Организация конвейера команд

Упрощенная схема конвейера команд

![]()

Конвейер команд процессора Pentium является пятиступенчатым, как и в предыдущей модели i486. Начиная со второй фазы декодирования (D2), конвейер становится параллельным, разделяясь на основной (U-конвейер) и вспомогательный (V-конвейер).

U-конвейер может выполнять любые целочисленные команды и команды FPU. Имеется ответвление от фазы ЕХ для трехступенчатого FPU-конвейера. V-конвейер может выполнять простые целочисленные команды и команду обмена FPU – FXCH.

Выделение команды FXCH для спаривания с другими командами FPU связано с довольно частым ее использованием для перестановки данных в регистрах FPU. Регистры данных FPU (8 регистров по 80 бит каждый) организованы как регистровый стек. Команды FPU по умолчанию используют операнды из вершины стека и помещают результат операции также в вершину стека. В отличие от организации стека в памяти, использование операнда из вершины стека, а также запись результата в вершину не сопровождаются инкрементом или декрементом указателя вершины стека. Этот указатель является трехбитным и размещается в управляющем регистре FPU – CR.

Описание фаз конвейера

1) Фаза PF (Pre Fetch) – предварительная выборка команд. На стадии PF процессор осуществляет выборку команд программы из кэш-памяти команд или (при кэш-промахе) из ОП.

Блок предварительной выборки (PFU) содержит два буфера емкостью по 32 байта каждый (емкость буфера совпадает с длиной блока (строки) кэш-памяти).

В любой момент времени выборка команд производится только в один из буферов. При этом выборка команд осуществляется по последовательным адресам. Если в выбираемом фрагменте машинной программы встречается команда ветвления, то определение дальнейшего направления выборки команд осуществляется с помощью ВТВ. ВТВ выдает адрес наиболее вероятного перехода на основании двухбитовой предыстории переходов.

Если предсказание соответствует случаю отсутствия перехода, то последовательная выборка команд продолжается. Если же имеет место предсказанный переход (нарушение последовательности адресов выполняемых команд), то происходит переключение на другой буфер, в который осуществляется выборка команд по новому адресу, полученному из ВТВ. Окончательное решение о правильности выбранного направления перехода переносится на стадию ЕХ команды условного перехода, на которой, собственно, и осуществляется анализ заданного в команде условия перехода.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.