"Pulse Voltage Source" "2KHz" "" "VPULSE" "1"

"Pulse Voltage Source" "4KHz" "" "VPULSE" "1"

"Voltage Source" "5Vpos" "" "VSRC" "1"

"Pulse Voltage Source" "8KHz" "" "VPULSE" "1"

"Pulse Voltage Source" "16KHz" "" "VPULSE" "1"

"Pulse Voltage Source" "32KHz" "" "VPULSE" "1"

"Header, 8-Pin" "JP1" "HDR1X8" "Header 8" "1"

"Triple 3-Input Positive-NOR Gate" "U1" "N014" "SN74LS27N" "1"

"Triple 3-Input Positive-NOR Gate" "U2" "N014" "SN74LS27N" "1"

"Triple 3-Input Positive-NOR Gate" "U3" "N014" "SN74LS27N" "1"

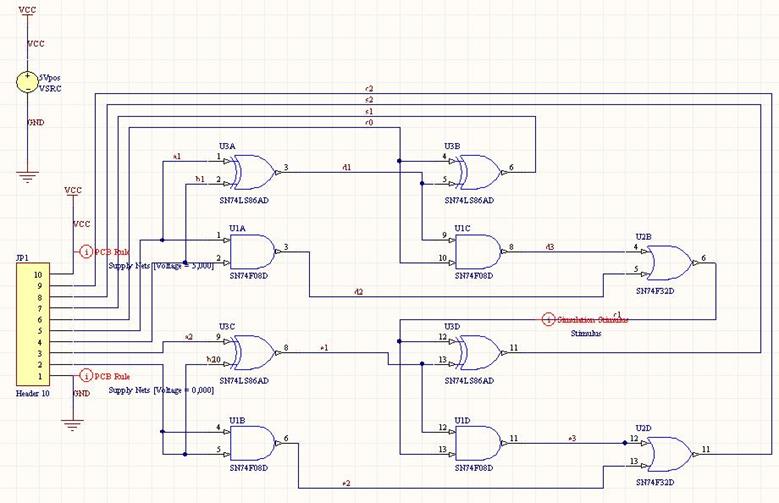

Для проекта «Сумматор»

Схема электрическая

Список цепей схемы в формате spice

Сумматор

*SPICE Netlist generated by Advanced Sim server on 03.04.2010 19:39:56

*Add Node Bridge Data

ADVB1 [A1$DV A2$DV B1$DV B2$DV C0$DV C1$DV C2$DV D1$DV D2$DV D3$DV E1$DV]

+ [A1 A2 B1 B2 C0 C1 C2 D1 D2 D3 E1] dav_mod

ADVB2 [0 VCC][GND$AD VCC$AD] adc_mod

ADVB3 [VCC$DA][VCC] dac_mod

ADVB4 [E2$DV E3$DV S1$DV S2$DV][E2 E3 S1 S2] dav_mod

.model adc_mod xadc

.model dac_mod xdac

.model dav_mod xdav

*Schematic Netlist:

V5Vpos VCC 0 +5

AU1A [VCC$AD GND$AD A1$DV B1$DV ][VCC$DA A1$DV B1$DV D2$DV ]SN74F08

AU1B [VCC$AD GND$AD B2$DV B2$DV ][VCC$DA B2$DV B2$DV E2$DV ]SN74F08

AU1C [VCC$AD GND$AD D1$DV C0$DV ][VCC$DA D1$DV C0$DV D3$DV ]SN74F08

AU1D [VCC$AD GND$AD E1$DV C1$DV ][VCC$DA E1$DV C1$DV E3$DV ]SN74F08

AU2B [VCC$AD GND$AD D3$DV D2$DV ][VCC$DA D3$DV D2$DV C1$DV ]SN74F32

AU2D [VCC$AD GND$AD E3$DV E2$DV ][VCC$DA E3$DV E2$DV C2$DV ]SN74F32

AU3A [VCC$AD GND$AD A1$DV B1$DV ][VCC$DA A1$DV B1$DV D1$DV ]SN74LS86

AU3B [VCC$AD GND$AD C0$DV D1$DV ][VCC$DA C0$DV D1$DV S1$DV ]SN74LS86

AU3C [VCC$AD GND$AD A2$DV B2$DV ][VCC$DA A2$DV B2$DV E1$DV ]SN74LS86

AU3D [VCC$AD GND$AD C1$DV E1$DV ][VCC$DA C1$DV E1$DV S2$DV ]SN74LS86

.SAVE 0 A1 A2 B1 B2 C0 C1 C2 D1 D2 D3 E1 E2 E3 S1 S2 VCC V5Vpos#branch @V5Vpos[z]

.SAVE @V5Vpos[p]

*PLOT TRAN -1 1 A=A1 A=A2 A=B1 A=B2 A=C0 A=C1 A=C2 A=D1 A=D2 A=D3 A=E1 A=E2 A=E3

*PLOT TRAN -1 1 A=S1 A=S2

*PLOT OP -1 1 A=A1 A=A2 A=B1 A=B2 A=C0 A=C1 A=C2 A=D1 A=D2 A=D3 A=E1 A=E2 A=E3

*PLOT OP -1 1 A=S1 A=S2

*Selected Circuit Analyses:

.TRAN 2E-8 5E-6 0 2E-8

.OP

*Models and Subcircuit:

.MODEL SN74F08 xsimcode(file="C:\PROGRAM FILES\ALTIUM\Library\Sim\FAST.SCB" func=f08

+ )

.MODEL SN74F32 xsimcode(file="C:\PROGRAM FILES\ALTIUM\Library\Sim\FAST.SCB" func=f32

+ )

.MODEL SN74LS86 xsimcode(file="C:\PROGRAM FILES\ALTIUM\Library\Sim\LS.SCB" func=ls86

+ )

.END

Список параметров электрических цепей схемы NetList Status

Nets report For

On 24.04.2010 at 13:18:10

A1 Signal Layers Only Length:84 mms

A2 Signal Layers Only Length:57 mms

B1 Signal Layers Only Length:93 mms

B2 Signal Layers Only Length:89 mms

C0 Signal Layers Only Length:92 mms

C1 Signal Layers Only Length:55 mms

C2 Signal Layers Only Length:52 mms

D1 Signal Layers Only Length:45 mms

D2 Signal Layers Only Length:28 mms

D3 Signal Layers Only Length:17 mms

E1 Signal Layers Only Length:56 mms

E2 Signal Layers Only Length:37 mms

E3 Signal Layers Only Length:23 mms

GND Signal Layers Only Length:55 mms

S1 Signal Layers Only Length:68 mms

S2 Signal Layers Only Length:87 mms

VCC Signal Layers Only Length:60 mms

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.