Федеральное агентство по образованию

Государственное образовательное учреждение высшего профессионального образования

«Владимирский государственный университет»

Кафедра Конструирования и технологии радиоэлектронных средств

Отчет по лабораторной работе №3

по дисциплине ИТПРЭС

Работу выполнил: студент гр. Р-106

Работу принял: доц.каф. КТРЭС

Владимир 2010

Задание на лабораторную работу.

Выполнить логическое моделирование (анализ переходных процессов).

Выполнить логическое моделирование.

Протокол работы.

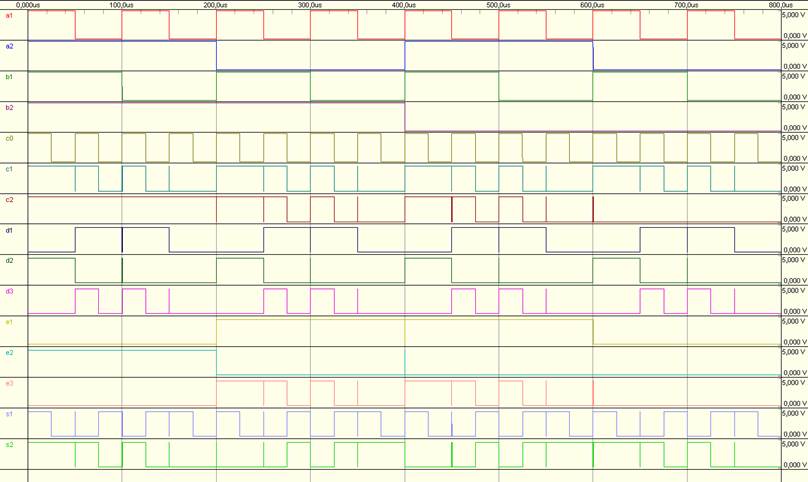

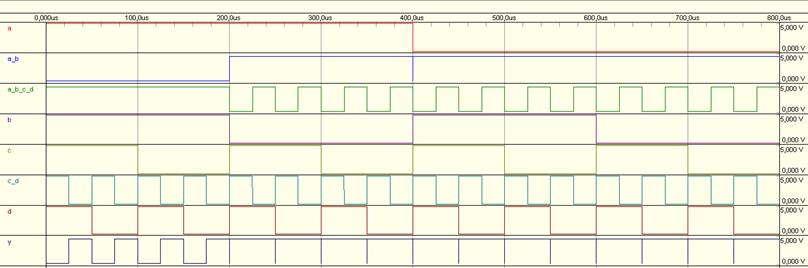

Выходные характеристики логической цепи:

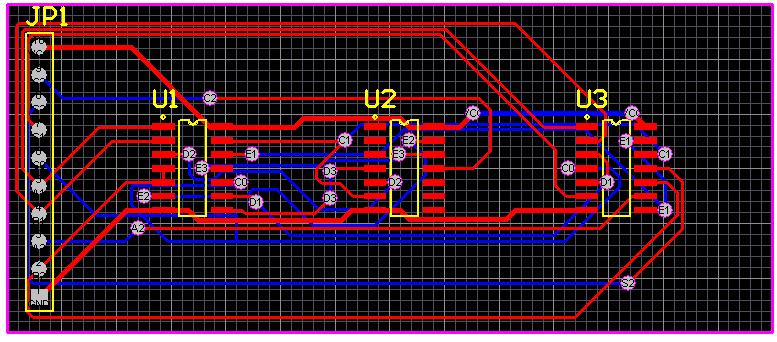

Трассировка схемы проекта «Сумматор»:

Посттопологический анализ схемы проекта «Сумматор»:

Возникшие ошибки и их решения:

1. Ошибки при моделировании «Логической цепи, состоящей из элементов 4ИЛИ-НЕ»

Причина: отсутствие у элемента логической модели.

Решение: выбор элементов с наличием логическим описанием в своей библиотеке.

2. Ошибки, говорящие о невозможности проведения анализа целостности сигналов для проекта «Сумматор».

Причина: отсутствие ссылок на некоторые компоненты схемы (component link).

Решение: Запуск Project \ Component Link. Но при попытке исправить схему сумматора для уменьшения помех, это решение не подошло:

Документы, полученные в ходе выполнения лабораторной работы.

Проект «Логическая цепь 4ИЛИ-НЕ»

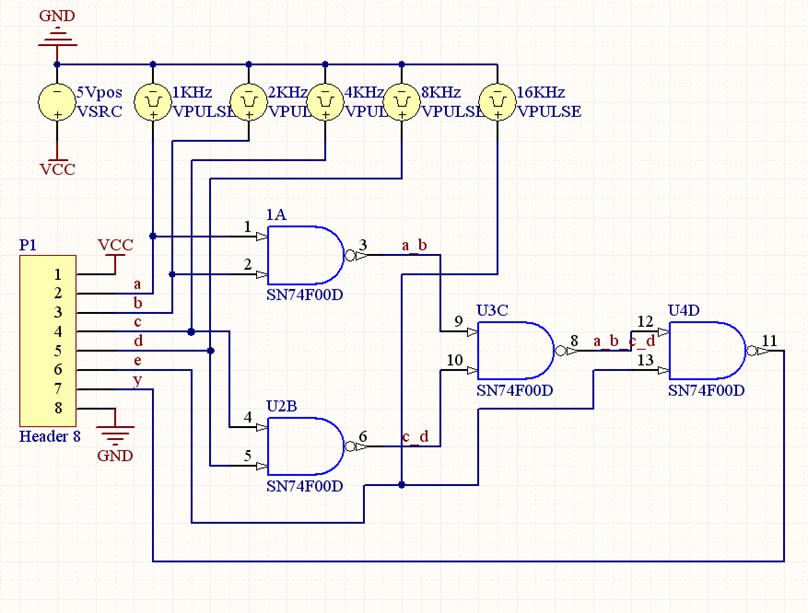

Схема электрическая

Логический анализ цепи

Список цепей схемы в формате spice

Логическая цепь

*SPICE Netlist generated by Advanced Sim server on 02.04.2010 19:28:25

*Add Node Bridge Data

ADVB1 [Net16KHz_1$DA Net1KHz_1$DA Net2KHz_1$DA Net32KHz_1$DA Net4KHz_1$DA]

+ [Net16KHz_1 Net1KHz_1 Net2KHz_1 Net32KHz_1 Net4KHz_1] dac_mod

ADVB2 [0 Net16KHz_1 Net1KHz_1 Net2KHz_1 Net32KHz_1 Net4KHz_1 Net8KHz_1]

+ [GND$AD Net16KHz_1$AD Net1KHz_1$AD Net2KHz_1$AD Net32KHz_1$AD Net4KHz_1$AD Net8KHz_1$AD] adc_mod

ADVB3 [VCC][VCC$AD] adc_mod

ADVB4 [Net8KHz_1$DA VCC$DA][Net8KHz_1 VCC] dac_mod

ADVB5 [G$DV H$DV Выход$DV][G H Выход] dav_mod

.model adc_mod xadc

.model dac_mod xdac

.model dav_mod xdav

*Schematic Netlist:

V1KHz Net1KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 400us 800us) AC 5 0

V2KHz Net2KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 200us 400us) AC 5 0

V4KHz Net4KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 100us 200us) AC 5 0

V5Vpos VCC 0 +5

V8KHz Net8KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 50us 100us) AC 5 0

V16KHz Net16KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 25us 50us) AC 5 0

V32KHz Net32KHz_1 0 DC 0 PULSE(0 5 0 50n 50n 12.5us 25us) AC 5 0

AU1A [VCC$AD GND$AD Net1KHz_1$AD Net2KHz_1$AD Net4KHz_1$AD ][VCC$DA Net1KHz_1$DA

+ Net2KHz_1$DA Net4KHz_1$DA G$DV ]SN74LS27

AU2B [VCC$AD GND$AD Net4KHz_1$AD Net8KHz_1$AD Net16KHz_1$AD ][VCC$DA Net4KHz_1$DA

+ Net8KHz_1$DA Net16KHz_1$DA H$DV ]SN74LS27

AU3B [VCC$AD GND$AD G$DV H$DV Net32KHz_1$AD ][VCC$DA G$DV H$DV Net32KHz_1$DA

+ Выход$DV ]SN74LS27

.SAVE 0 G H Net16KHz_1 Net1KHz_1 Net2KHz_1 Net32KHz_1 Net4KHz_1 Net8KHz_1 VCC

.SAVE Выход V16KHz#branch V1KHz#branch V2KHz#branch V32KHz#branch V4KHz#branch

.SAVE V5Vpos#branch V8KHz#branch @V16KHz[z] @V1KHz[z] @V2KHz[z] @V32KHz[z] @V4KHz[z]

.SAVE @V5Vpos[z] @V8KHz[z] @V16KHz[p] @V1KHz[p] @V2KHz[p] @V32KHz[p] @V4KHz[p]

.SAVE @V5Vpos[p] @V8KHz[p]

*PLOT TRAN -1 1 A=G A=H A=Выход

*PLOT OP -1 1 A=G A=H A=Выход

.OPTION KeepLastSetup=False

*Selected Circuit Analyses:

.TRAN 5E-7 0.004 0 5E-7

.OP

*Models and Subcircuit:

.MODEL SN74LS27 xsimcode(file="C:\PROGRAM FILES\ALTIUM\Library\Sim\LS.SCB" func=ls27

+ )

.END

Перечень элементов Bill Of Material

Description Designator Footprint LibRef Quantity

"Pulse Voltage Source" "1KHz" "" "VPULSE" "1"

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.