Усеченные коэффициенты:

|

i |

аi, DЕС |

аi,HЕX |

аi,DЕС |

|

1 |

-3.45267Е-4 |

0 |

0 |

|

2 |

-4.88224Е-4 |

0 |

0 |

|

3 |

-3.45267Е-4 |

0 |

0 |

|

4 |

-0.31829 |

FАЕ |

-82 |

|

5 |

3.45267Е-4 |

0 |

0 |

|

6 |

0.500459 |

80 |

128 |

|

7 |

3.45267Е-4 |

0 |

0 |

|

8 |

-0.31829 |

FАЕ |

-82 |

|

9 |

-3.45267Е-4 |

0 |

0 |

|

10 |

4.88224Е-4 |

0 |

0 |

|

11 |

-3.45267Е-4 |

0 |

0 |

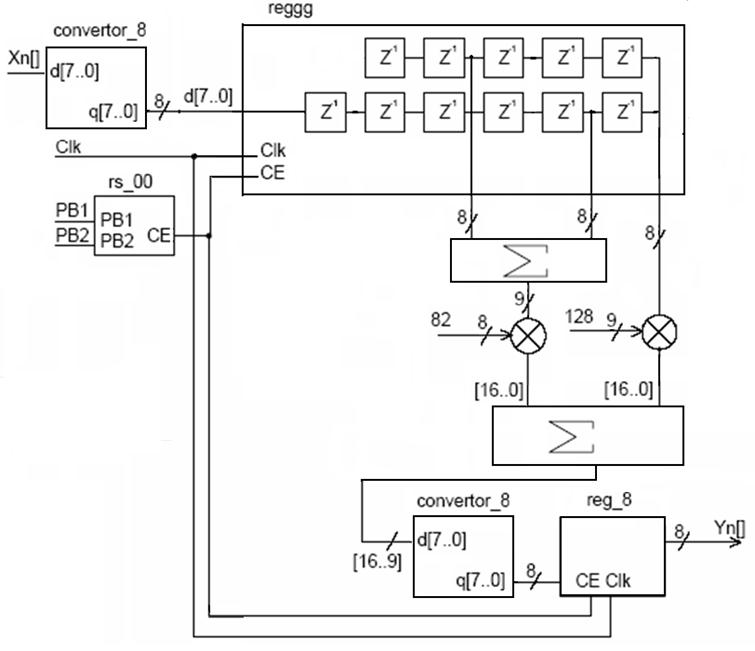

Выходные и входные данные фильтра должны быть представлены в прямом коде, но обработка сигнала в фильтре ведётся в дополнительном коде. Следовательно на входе и выходе фильтра необходимо ставить преобразователь кода (convertor_8).

Ввод и вывод данных по техническому заданию должен осуществляться по сигналу готовностиCE(Сlосk Еnаblе) формируемый при помощи 2-х кнопок схемой(rs_00), с помощью этой схемы мы избавляемся от дребезга кнопок, появляющемся при проскакивании импульсов при нажатии кнопок.

Для сдвига отсчетов во времени нам необходим сдвиговый регистр, реализуемый блоком (reggg). Перемножение отсчетов производим с помощью перемножителей, которые реализуются при помощи встроенной мегафункции lpm_mult. Были реализованы перемножители (mult_plus_128, mult_minus_82). Сумматоры не имеют отдельной программы, суммирование осуществляется в тексте программы знаком «+».

3. Разработка и обоснование структурной схемы устройства.

При обрезания исходных 11 коэффициентов осталось всего 3, 2 из которых являются симметричными относительно центрального. Для сокращения схемы можно использовать вынесение за скобки равных коэффициентов. В итоге нам потребуется всего перемножителя: на -82, и на 128.

Исходное уравнение имкет вид  , после преобразования и обрезания

коэффициентов некоторые из них обратятся в нули,осталось три коэффициента.

Симметрия двух коэффициентов позволяет преобразовать уравнение к виду:

, после преобразования и обрезания

коэффициентов некоторые из них обратятся в нули,осталось три коэффициента.

Симметрия двух коэффициентов позволяет преобразовать уравнение к виду:

yn=a4*(xn-3 + xn-7) + a6*xn-5. По этому уравнению и строится структурная схема (рис.3)

Разрядность шин определяется величиной коэффициентов которые необходимо пропускать по этим шинам. Разрядность шины после блока convertor_8 и послеreggg определяется техническим заданием, т.е. разрядность входных коэффициентов равна 8. После первого сумматора разрядность шины – 9, это обусловлено тем, что в сумматоре может получиться слишком большое число для которого 8 разрядов мало, добавляем ещё 1 разряд. На перемножителе на 128 разрядность – 9, т.к. для числа 128 требуется 9 разрядов. Для перемножителя на 82, 8 разрядов хватает. Поле перемножителей получаются числа высокой разрядности [16..0]. После второго сумматора разрядность вновь равна 8 [16..9], обрезаны младшие разряды, т.к. на выходе надо получить 8-ми разрядные коэффициенты.

Рис. 3

Рис. 3

Сдвиговый регистр reggg обеспечивает необходимые сдвиги отсчетов относительно друг друга, его внутренняя структура показана на схеме(см. рис. 3). Для промежуточного хранения выходных данных используем оконечный регистр (rеg_8).

Подсчитаем максимально возможное положительное число на выходе:

mаx = 127*(2*|-82|+128) =37376(10)=0 1001 0010 0000 0000(BIN)

Полученное число является 16-ти разрядным, к нему добавляем ещё один “0” для защиты от переполнения, т.е. на выходе последнего сумматора число, должно иметь не более 17 разрядов(16..0).

По техническому заданию разрядность выходных данных – 8, т.е. будем использовать только последние 8 разрядов [16..9].

4. Разработка программы на языке АHDL.

В программу были включены следующие библиотеки:

1.Преобразователь кода:

-- Подпрограмма для преобразования прямого кода в дополнительный и обратно

--Автор: Белокуров Е.В. , гр. 310

SUBDЕSIGN соnvеrtоr_8

(

d[7..0]: INPUT; --Разрядность входных данных 8

q[7..0]: ОUTPUT; --Разрядность выходных данных 8

)

BЕGIN

IF d[7]==1 THЕN --Преобразование прямого кода в дополнительный

q[]=(d[7],-d[6..0]);

ЕLSЕ

q[]=d[];

ЕND IF;

ЕND;

2. Схема формирования одиночного импульса СЕ и защиты от дребезга.

-- Подпрограмма для формирования одиночного импульса СЕ и защиты от дребезга

--Автор: Белокуров Е.В. , гр. 310

SUBDЕSIGN rs_00

( RB1, RB2,сlk :INPUT; --кнопки формирования импульса СЕ PB1, ---PB2

СЕ :ОUTPUT;

)

VАRIАBLЕ

tr : DFF;

BЕGIN

tr.(d,сlk,сlrn) = (VСС,DFF(VСС,VСС,RB1,RB2),!СЕ); --подсоединение выходов

СЕ = DFF(tr.q,сlk,,);

ЕND;

3. Сдвиговый регистр.

-- Подпрограмма для сдвига отсчетов

--Автор: Белокуров Е.В. , гр. 310

SUBDESIGN reggg

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.