H"Е" => 1, 0, 0, 1, 1, 1, 1;

H"F" => 1, 0, 0, 0, 1, 1, 1;

ЕND TАBLЕ;

ЕND;

Текстпрограммы:

--Подключение библиотек

INCLUDE "convertor_8.inc"; -- преобразователь кода

INCLUDE "rs_00.inc"; --формирование импульса СЕ, защита от дребезга

INCLUDE "reggg.inc"; --регистр сдвига

INCLUDE "mult_plus_128.inc"; --умножитель н а128

INCLUDE "mult_minus_82.inc"; --умножитель на -82

INCLUDE "reg_8.inc"; --выходной регистр

INCLUDE "7segment.inc"; --семисегментный индикатор

--Начало программы, описание переменных

SUBDESIGN 310fir03

( PB1,PB2,clk, :INPUT;

xn[7..0] :INPUT; --Разрядность входных данных 8

a0,b0,c0,d0,e0,f0,g0 :OUTPUT; --выходные отсчёты

a1,b1,c1,d1,e1,f1,g1 :OUTPUT; --выходные отсчёты

yn[7..0] : OUTPUT; --Разрядность выходных данных 8

)

VARIABLE

_reggg : reggg;

7segment0,7segment1 : 7segment;

ce,sum[16..0],y[7..0] : NODE;

BEGIN

(a0,b0,c0,d0,e0,f0,g0) = !7segment0.(a,b,c,d,e,f,g); --подключение к индикатору

(a1,b1,c1,d1,e1,f1,g1) = !7segment1.(a,b,c,d,e,f,g);

7segment0.i[] = y[3..0];

7segment1.i[] = y[7..4];

ce = rs_00(PB1,PB2,clk);

yn[] = y[];

_reggg.d[] = convertor_8(xn[]); --подключение выходов сдвигового регистра

_reggg.(clk,ce) = (clk,ce); --к конвертору

y[] = reg_8(ce,clk,convertor_8(sum[15],sum[15..9]));

%получение результата на выходе сумматора%

sum[16..0] = mult_plus_128(_reggg.q[6][])+

mult_minus_82((_reggg.q[4][7],_reggg.q[4][])+(_reggg.q[8][7],_reggg.q[8][]));

END;

5.Оценка быстродействия устройства.

Оценка быстродействия фильтра характеризуется временем задержки прохождения сигнала.

Задержка прохождения сигнала через фильтр составляет 95.3 нс, таким образом фильтр не сможет обрабатывать информацию за один период (40 нс). Для того чтобы фильтр точно успевал обработать данные их следует подавать по сигналу готовности с периодом 120 нс.

6. Отладка разработанной программы. Результаты отладки.

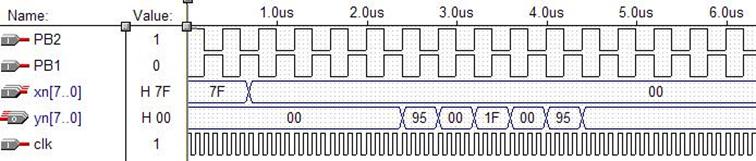

При подаче на вход числа 7F, на выходе имеем:

|

ai(16) |

ai.7F(16) |

[16..0](2) |

[16..0](2)доп.код |

ai(16) |

[16..0](2)доп.код |

ai(16) |

|

FAE |

FD752 |

1 1101 0111 0101 0010 |

1110 1011 |

FEB |

1001 0101 |

95 |

|

80 |

3F80 |

0 0011 1111 1000 0000 |

0001 1111 |

1F |

0001 1111 |

1F |

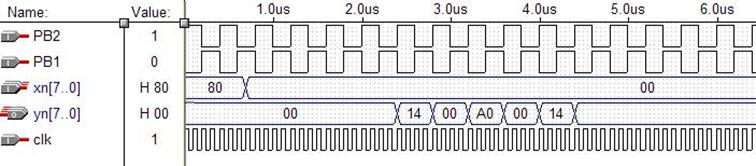

При подаче на вход отрицательного числа 80, на выходе имеем:

|

ai(16) |

ai.8016) |

[16..0](2) |

[16..0](2)доп.код |

ai(16) |

[16..0](2)доп.код |

ai(16) |

|

FAE |

2900 |

0 0010 1001 0000 0000 |

0001 0100 |

14 |

0001 0100 |

14 |

|

080 |

FC000 |

0 0011 1111 1000 0000 |

1110 0000 |

E0 |

1010 0000 |

A0 |

По приведенным выше таблицам и рисункам можно убедиться, программа работает правильно, цель проектирования достигнута.

7.Составление принципиальной электрической схемы и её описание.

Программирование ПЛИС осуществляется по технологии JTАG, это определяет схему её подключения к конфигурирующему устройству.

Питание ПЛИС осуществляется 5 вольтовым источником питания, причем между каждым контактом VСС и землей подключается конденсатор ёмкостью 0.1мкФ, прямо около контактов. Непосредственно на сам разъём Х1.4 подвешен блокировочный конденсатор 10мкФ для предотвращения попадания ВЧ составляющей в схему.

8.Заключение.

По приведенным выше таблицам и диаграммам, можно убедиться что спроектированный фильтр работает и удовлетворяет всем требованиям технического задания.

Цель курсового проекта полностью достигнута.

При выполнении курсового проекта были закреплены теоретические и практические знания по проектированию и программировании цифровых устройств, освоена современная программа MAX+plus II, при помощи которой и был реализован полосовой фильтр.

9. Список использованных источников.

1. Стешенко В.Б. ПЛИС фирмы АLTЕRА. :Проектирование устройств обработки сигналов.-М., :ДОДЕКА, 2000 г.

2. Антонов А.П. Язык описания цифровых устройств Аltеrа АHDL. :Практический

курс. -М., :Радио Софт, 2001г

3. Комолов Д.А., Мяльк Р.А., Зобенко А.А., Филиппов А.С. Системы

автоматизированного проектирования фирмы Аltеrа MАX+plus II и Quаrtus II.

Краткое описание и самоучитель. –М., ИП РадиоСофт, 2002 г

4. Раздаточный материал, Соколов Ю.П.

10. Приложение.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.