К сожалению, такая структура не всегда позволяет реализовать требуемую конфигурацию. В сложных устройствах с большим числом длинных нерегулярных связей удается использовать не более 50% ресурсов кристалла.

В некоторых сериях предусмотрена настройка на логические уровни сигналов, характерные для ИМС структуры КМОП или ТТЛ.

Логические ИС, часть 2

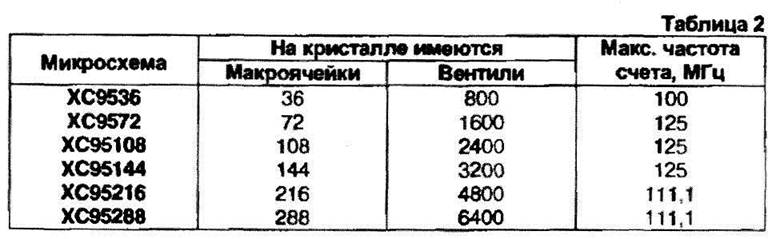

По сравнению с FPGA, структура CPLD более "крупнозерниста". Рассмотрим ее на примере микросхем серии XC9S0G, структурная схема которых приведена на рис.7, а сведения о составе - в табл.2.

|

|

Указанные там же максимальные частоты относятся к 16 разрядным двоичным счетчикам, реализованным на таких ПЛИС. Следует иметь в виду что рассматриваемая серия - сравнительно медленная. Счетчикииз элементов других ПЛИС способны работать на частотах до 350 МГц.

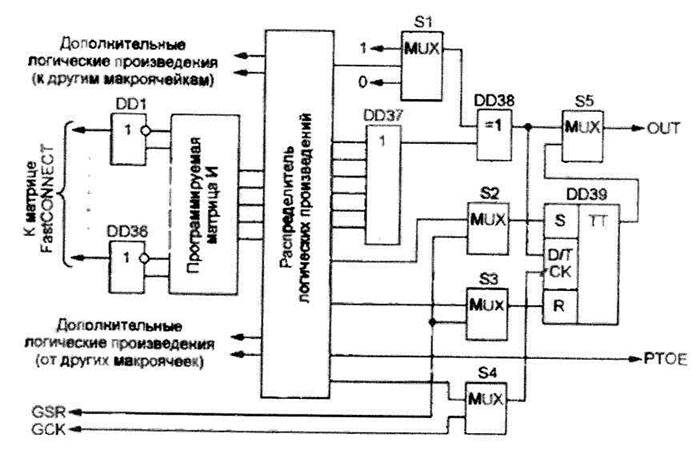

Схема макроячейки логического блока ПЛИС серии ХС9500 приведена на рис.8. С помощью программируемой матрицы И формируют до пяти логических произведений 36-ти переменных, еще два произведения можно взять от соседних макроячеек.. На выходе элемента ИЛИ (DD37) обоазуется логическая сумма этих произведений, которая поступает на вход переключателя S5 и триггера DD39 в прямом или проинвертированном виде в зависимости от положений программируемого переключателя S1. В одном из положений последнего инверсией управляет сигнал, сформированный в распределителе логических произведений. Сигналами с других выходов распределителя тактируют, устанавливают и сбрасывают триггер DD39. Изменив положение переключателей S2-S4, эти функции можно выполнять с помощью глобальных сигналов синхронизации и сброса, поступающих непосредственно с выводов ПЛИС.

В составе БВВ ПЛИС серии ХС9500 имеются только буферы ввода и вывода, триггеров в них нет. Перевести выход БВВ в активное состояние можно с помощью сигнала РТОЕ, поступающего от макроячейки, либо одного из глобальных сигналов GOE1 - GOE4, формируемых специальным программируемым логическим блоком из входным сигналов ПЛИС.

Рис.8.

Цепи OUT и РТОЕ каждой макроячейки ПЛИС CPLD связаны только с одним блоком ввода/вывода, который в свою очередь соединен с определенным внешним выводом. В FPGA такой жесткой связи нет.

Соединения функциональных блоков между собой и с входными цепями БВВ реализуют с помощью программируемой коммутационной матрицы, фирменное название которой FastCONNECT можно перевести как "быстрое соединение". Матрица обладает регулярной структурой, обеспечивает одинаковую задержку распространения всех сигналов и, самое главное, гарантирует трассировку всех необходимых связей. Последнее позволяет произвольным образом распределять по выводам ПЛИС внешние цепи разрабатываемого устройства.

Приступая к проектированию устройства на ПЛИС, следует подготовить его схему с помощью любого их известных схемных редакторов, например, популярного ORCAD. При этом нет необходимости разбираться в тонкостях логической организации ПЛИС. Устройства создают из типовых логических элементов, триггеров, буферов, мультиплексоров, сумматоров, дешифраторов, счетчиков, регистров сдвига, в том числе - эквивалентов распространенных микросхем серии 74 (отечественный аналог - серия К155).

Фирма X1L-INX предлагает разработчикам готовые библиотеки таких элементов, а задачу "упаковки" устройства в ПЛИС решает специализированная система автоматизированного проектирования (САПР) XILINX FOUNDATION. Кроме имени исходного файла со схемой, системе достаточно сообщить типы микросхемы и ее корпуса, Главный результат работы САПР - двоичный файл, предназначенный для загрузки в ПЛИС. Она создает и вспомогательные текстовые файлы, например, с описанием реализованного САПР распределения внешних цепей выводам ПЛИС.

Замечательная особенность XILINX FOUNDATION - встроенная программа логического моделирования, позволяющая на любом этапе ввода схемы проверить работу отдельных узлов, а затем и всего устройства. Достаточно назначить контрольные точки (входы и выходы), «подать» входные тестовые сигналы и просмотреть временные диаграммы выходных. При вводе сложных схем оперативное моделирование позволяет обнаружить и вовремя исправить грубые ошибки, Число контрольных точек может достигать тысячи.

Так как работа спроектированного устройства зависит не только от правильной реализации логических функций, но и от скорости переключения элементов и распространения сигналов, есть возможность выполнить моделирование с учетом задержек. Но эта операция доступна только после размещения всех элементов устройства на кристалле и полной трассировки связей. САПР снабжена программами автоматической упаковки типовых элементов в кристалл и трассировки связей. Дополнительно для ПЛИС многих типов предусмотрено «ручное управление» конфигурацией с помощью специального редактора. Однако эту трудоемкую работу следует предпринимать только в крайних случаях, если, например, необходимо добиться максимального быстродействий проектируемого устройства или САПР не справляется с задачей в автоматическом режиме.

Следует сказать, что фирменный пакет программ XILINX FOUNDATION стоит довольно дорого, и нет смысла приобретать его, чтобы спроектировать всего одно устройство.

В качестве альтернативы фирма предлагает бесплатную версию САПР, позволяющую делать все, за исключением последнего этапа - получения файла "прошивки" ПЛИС. Подготовленные и проверенные исходные данные рекомендуется отправлять по электронной почте на сайт фирмы XILINX , где их оттранслируют в загрузочный файл и вернут обратно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.